Narodziny sowieckiego systemu obrony przeciwrakietowej. Z czego zbudowano Elbrus-2?

Pozostaje nam wreszcie przyjrzeć się bohaterowi okazji – słynnej logice ECL, na której montowano Elbrus-2 i z którą w Unii były takie piekielne męki.

Idea logiki sprzężonej z emiterem jest dość prosta.

Logika DTL i TTL jest trudna do przetaktowania do wysokich częstotliwości ze względu na fakt, że tranzystory w cyklu pracy osiągają tryb nasycenia, z którego stosunkowo wolno wychodzą.

W rezultacie narodził się pomysł stworzenia układu, w którym tranzystory podczas przełączania pozostaną w trybie liniowym.

Mogą więc, z grubsza rzecz biorąc, włączać się nie do końca i bardzo szybko przełączać bieżące ścieżki.

Naturalnie doprowadziło to do tego, że różnica między poziomami logicznymi była bardzo mała według standardów logiki bipolarnej (rzędu 0,8 V, 3-4 razy mniej niż TTL), a obwód stał się bardzo wrażliwy na szumy i nagrzewanie które je wygenerowały (kłopot polegał na tym, że dzięki realizacji samego pomysłu schemat nie był dziecinnie rozgrzany).

Przełączanie poziomu dla każdego 1V wymaga zwykle około nanosekundy, dlatego tak trudno jest przetaktować TTL do prędkości większych niż 3–4 ns, a dla ECL 1–2 ns to prawie tryb pracy po wyjęciu z pudełka bez dodatkowych sztuczek ( tylko w obwodzie po wyjęciu z pudełka bez sztuczek wszyscy pochłoną hałas).

Co to jest ECL?

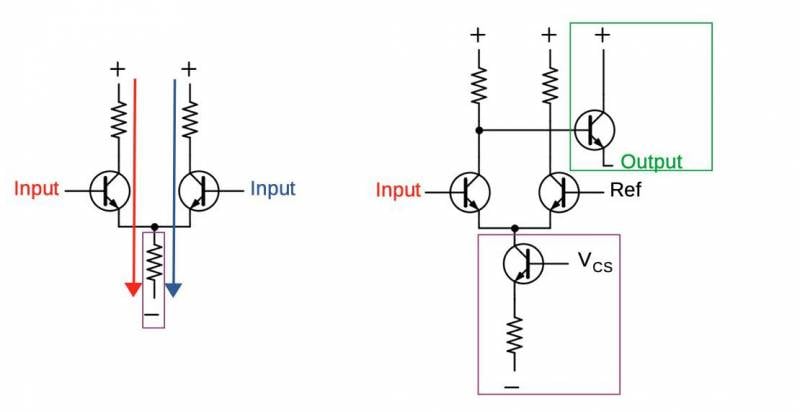

Możesz pozostawić klucz w trybie liniowym, używając nie tylko tranzystora wzmacniającego, ale pełnoprawnego wzmacniacza różnicowego.

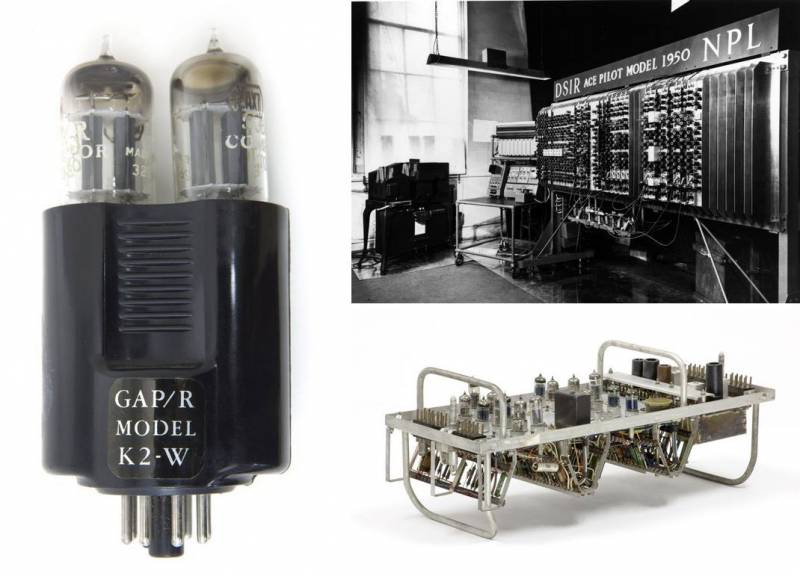

Co zabawne, ECL ma również swojego przodka w próżni, ponieważ taki trik można wykonać za pomocą kilku lamp. Obwód, nazwany później parą o długim ogonie lub różnicowym (różnicowy, od słowa „różnica”), został wynaleziony w Wielkiej Brytanii, w 1934 r. Pomysł został opublikowany przez wynalazcę-amatora Bryana Matthewsa, a w 1936 r. inżynier elektryk Alan złożył patent Blumlein (Alan Dower Blumlein).

Pod koniec lat trzydziestych topologia wzmacniaczy różnicowych była dobrze zrozumiana, a w komputerach ten proto-ECL był również pionierem brytyjskiego EDSAC (University of Cambridge Mathematical Laboratory, 1930), Pilot ACE (National Physical Laboratory, 1948) a kilka innych wczesnych maszyn, stworzonych przez kolegów Blumleina, zostało zmontowanych na różnicowych wzmacniaczach lampowych.

Ten obwód ma wiele zalet jako przełącznik: praktycznie odporny na fluktuacje lamp (ważne, jeśli twój obwód ma ich tysiące!), wysokie wzmocnienie i stabilność wzmocnienia, wysoka impedancja wejściowa, średnia/niska impedancja wyjściowa.

Generalnie było kwestią czasu, kiedy ten układ zostanie przystosowany do tranzystorów.

Zauważ, że opisaliśmy tylko najprostszy wzmacniacz różnicowy, w elektrotechnice jest to tak podstawowy obwód, jak każdy element NOR lub XOR w elektronice. Klasycznym rodzajem pilota zdalnego sterowania jest wzmacniacz operacyjny, który jest używany wszędzie, od komputerów analogowych po systemy stereo.

Wzmacniacz różnicowy działa dość prosto.

Przez obwód z dwoma ramionami przepływa stały prąd. Jeśli napięcie na lewym wejściu jest większe niż na prawym, włącza się lewy tranzystor, a większość prądu przechodzi przez lewą gałąź i odwrotnie.

Niewielka różnica między sygnałami wejściowymi generuje dużą zmianę prądu, stąd wzmacniacz.

Dodając parę tranzystorów bez problemu dostajemy lampę ze wzmacniacza. Aby to zrobić, musisz naprawić napięcie w jednym z ramion, nazywając to odniesieniem. Jeśli sygnał wejściowy jest większy niż odniesienie, uważany jest za „1”, a jeśli jest niższy - „0”. Zgodnie ze zwyczajem od czasów IBM, jako punkt odniesienia zwykle używa się poziomu gruntu.

W efekcie mamy bardzo, bardzo szybki obwód, który jest niestabilny na zakłócenia, zużywa dużo energii i tak samo się nagrzewa. Z dwóch ostatnich powodów trudno jest zwiększyć poziom integracji układów ECL - kilka miliardów tranzystorów CMOS będzie mniej się nagrzewać i zajmować mniej miejsca niż 50 XNUMX ECL.

Praca Motoroli i Fairchild była poświęcona przezwyciężeniu tych ograniczeń.

Pierwszym komputerem zmontowanym na ECL był, jak już powiedzieliśmy, potężny IBM 7030 Stretch, w rzeczywistości został stworzony dla niego.

IBM chciał wypuścić prawdziwego giganta, przewyższającego najszybsze komputery w tym czasie 10-12 razy, oczywiście żaden znany już układ nie był do tego odpowiedni.

Innowacją Stretcha była logika sprzężona z emiterem, stworzona przez inżyniera IBM, Hannona S. Yourke. Przełącznik Yurkego był wzmacniaczem różnicowym z dwoma logicznymi poziomami odniesienia 3 V i wymagał naprzemiennych dwóch stopni npn i pnp.

Schemat ten został wykorzystany nie tylko w 7030, ale także w naukowym 7090, a później - w postaci GIS w superkomputerze dla NASA System 360 model 91.

Na początku lat 1960. opracowano wiele obwodów logicznych sprzężonych z emiterem, w tym warianty z diodami Zenera, które eliminowały potrzebę stosowania 2 rodzajów tranzystorów.

Wersja IBM dla S/370 (a nie oszczędzali pieniędzy i używali ECL dosłownie wszędzie w drugiej linii komputerów mainframe), w postaci mikroukładu, nosiła nazwę CSEF (Current-Switch Emitter Follower).

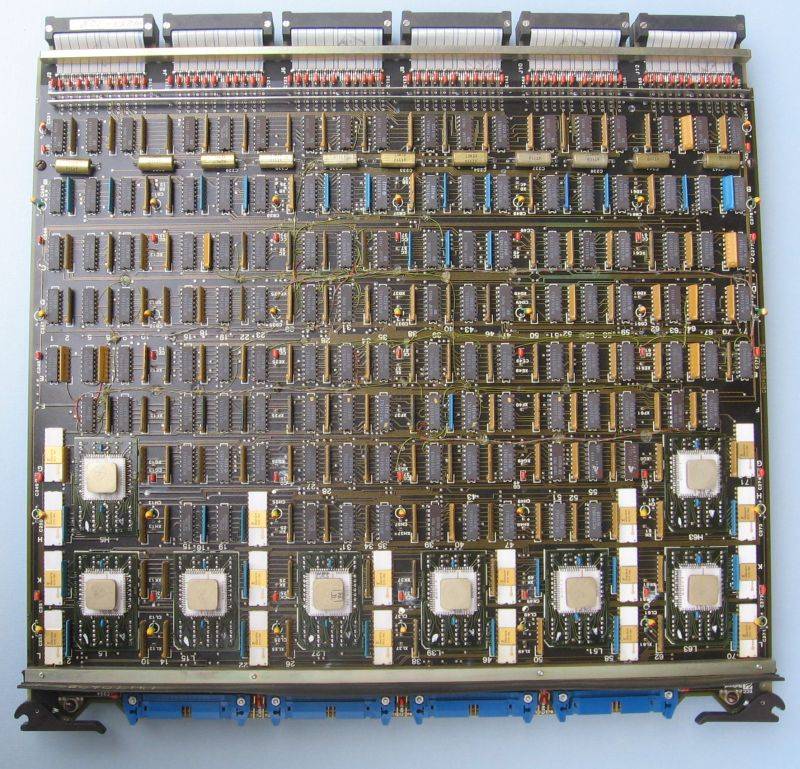

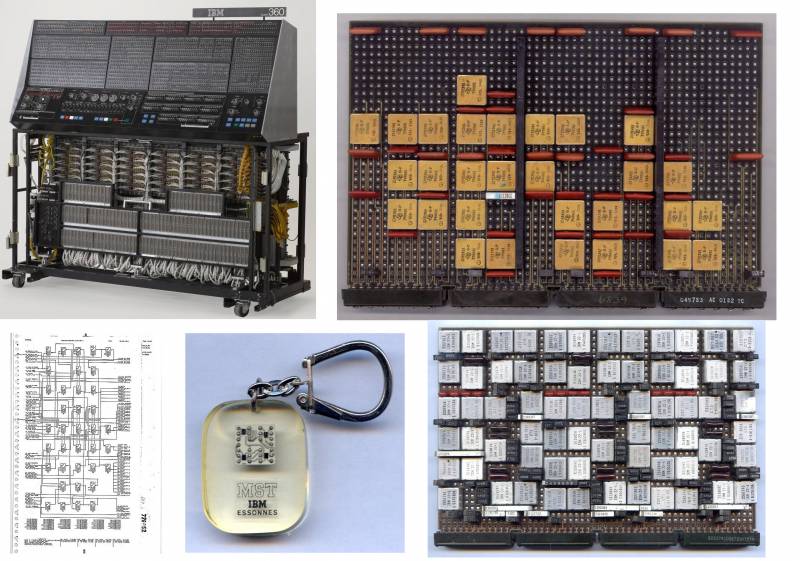

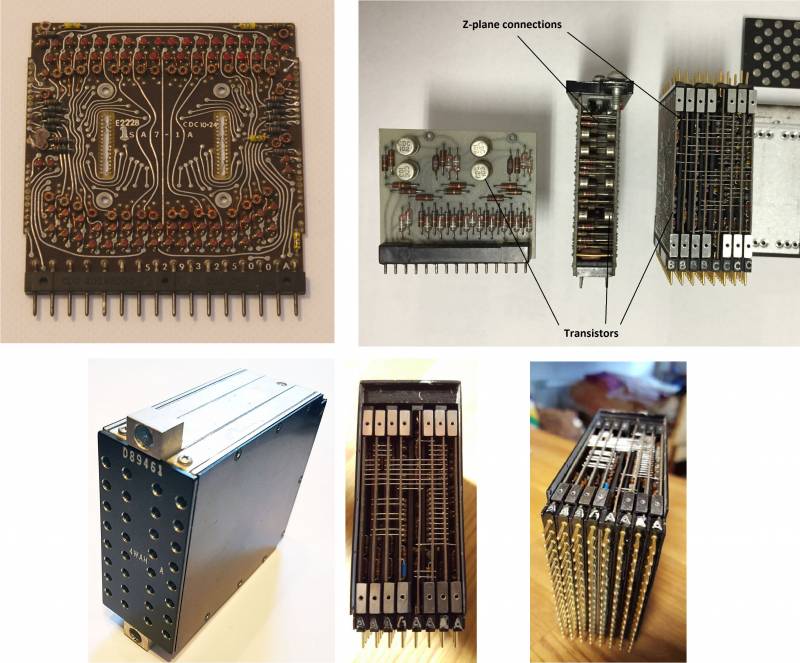

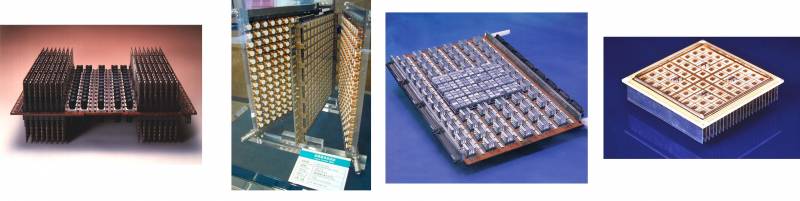

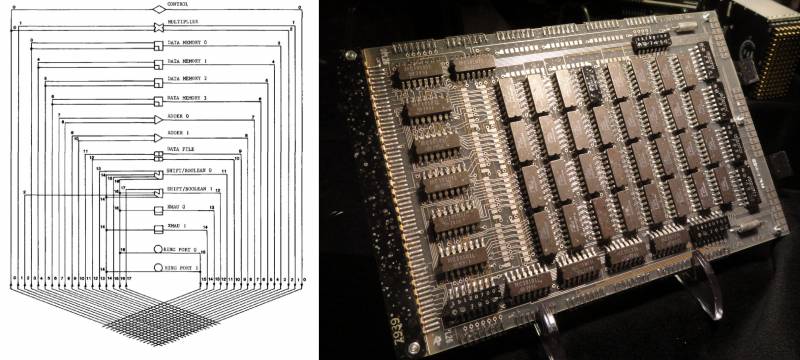

Na dole: schemat logiczny ALD (Automated Logic Diagram) stworzony przez oprogramowanie IBM EDA (Electronic Design Automation) do komputerowego wspomagania projektowania obwodów logicznych. Markowy brelok z chipem MST, 4 chipy IC są wyraźnie widoczne. Karta MST procesora mainframe IBM System/370 model 145 z 1982 roku. Każdy chip na nim zawierał do 5 chipów ECL i zastąpił całą płytę S/360. Kopiarki sowieckie z NITsEVT próbowały w latach 1980. iść prawie tą samą ścieżką, aby zastąpić całą TEZ jednym BMK

(http://ibm-1401.info, http://ummr.altervista.org/).

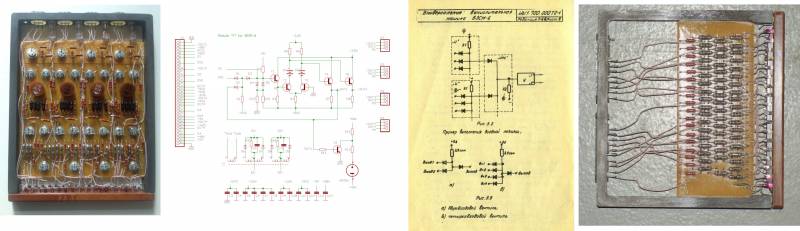

Sowiecką odpowiedzią na IBM 7030 był BESM-6, który był montowany na dość wyrafinowanej wersji ECL.

Problem, przed którym stanęli twórcy, był ogólnie taki sam: zwiększenie wydajności bez nadmiernego komplikowania obwodu, ale była jedna specyficzna cecha - nędza bazy elementów domowych.

W połowie lat 60. przemysł radziecki był w stanie wyprodukować tylko dwa szybkie urządzenia półprzewodnikowe: diodę D18 i tranzystor P416. A te były dość kiepskiej jakości. Musiałem wymyślić sprytne obwody.

Istotę opisuje jeden z projektantów BESM-6 V.N. Laut:

Czy można było na nich opracować elementy do wysokowydajnej maszyny?

... Do tego czasu w specjalistycznej literaturze pojawiło się wiele doniesień na temat wykorzystania diod tunelowych jako podstawy szybkich obwodów logicznych. Diody te miały krótkie czasy przełączania, wielokrotnie lepsze niż tranzystory.

Jednak elementy oparte na diodach tunelowych okazały się mieć słabą obciążalność, co doprowadziło do komplikacji obwodów maszynowych i szybko z nich zrezygnowaliśmy…

Trudność w stosowaniu tranzystorów polegała na tym, że były one bardzo wolne w trybie nasycenia, a elementy logiczne z nienasyconymi triodami okazały się skomplikowane ze względu na konieczność dopasowania poziomów sygnałów wejściowych i wyjściowych.

I nie tylko skomplikowane, ale i zawodne.

Przez jakiś czas nie widzieliśmy wyjścia z impasu.

Potrzebny był schemat zasilania, aby zminimalizować liczbę zawodnych tranzystorów, a jego kluczowy element został wymyślony przez tego samego Sokołowa, który później zmontował MCP dla Burcewa (a zespół BESM-6 podzielił się po śmierci Lebiediewa, po Mielnikowie lub Burcewie).

Na przykład, do tego celu można wykorzystać miniaturową baterię z zegarka elektronicznego.

Włączenie baterii między kolektor tranzystora a obciążenie kolektora (rezystor) sprawiło, że przełącznik stał się elementem o stałych poziomach sygnałów wejściowych i wyjściowych, a autonomicznemu źródłu zasilania nie nałożono żadnych szczególnie trudnych wymagań.

Oczywiście baterii nie dało się zainstalować, ponieważ w końcu się rozładowałaby, więc w rzeczywistym obwodzie został zastąpiony przez maleńki prostownik, składający się z miniaturowego transformatora na pierścieniu ferrytowym, dwóch diod półprzewodnikowych i kondensatora.

Nazwali te prostowniki „zasilaczami podwieszanymi” (PIP).

Wyjścia parafazowe wyłączników prądowych, wyposażone w wtórniki emiterowe, mogą pracować na wejściach układów logicznych „AND”, „OR”.

Pojawiły się następujące układy: pasywna logika kombinatoryczna oparta na elementach diodowo-rezystorowych została podłączona do wejść wzmacniających elementów aktywnych, których wyjścia z kolei zostały połączone z wejściami układów kombinatorycznych itp.

Tak więc korpus elektroniczny maszyny wyglądał jak tort warstwowy: warstwy diodowych obwodów logicznych były przeplatane warstwami wzmacniaczy na przełącznikach prądu.

Taka konstrukcja bardzo nadawała się do realizacji kolejnego niezwykle potężnego pomysłu - „pracy montażowej”.

W tym celu sygnały synchronizacji zostały również wprowadzone na wejście wzmacniaczy, które pełnią funkcję wyzwalaczy.

Z lekką ręką Siergieja Aleksiejewicza Lebiediewa obwody przenośników zaczęto nazywać w naszym kraju „zaopatrzeniem w wodę”.

BESM-6 była pierwszą radziecką maszyną wykorzystującą pracę przenośnika. Szybkość potoku, określona przez częstotliwość sygnałów synchronizacji, w BESM-6 wynosiła 10 MHz.

Tak więc opracowano zupełnie nowy system elementów logicznych, który pozwala wycisnąć maksymalną prędkość z dostępnych, niezbyt wysokiej jakości domowych tranzystorów i diod.

Wtedy konieczne stało się opracowanie konstrukcji takiej maszyny, aby nie tracić potencjalnej szybkości elementów logicznych, a także technologicznej i łatwej w obsłudze.

W latach 50. nie było wielowarstwowych płytek drukowanych szeroko stosowanych w nowoczesnych konstrukcjach komputerowych.

W BESM-6 płytki drukowane (dwustronne) były stosowane tylko w ogniwach (TEZ), które były dwojakiego rodzaju: z aktywnymi elementami wyzwalającymi i pasywnymi obwodami kombinatorycznymi.

Ogniwa aktywne miały na końcach sygnalizatory świetlne i zostały zainstalowane z przodu szafy, tworząc rodzaj panelu świetlnego, ogniwa pasywne umieszczono z tyłu szaf.

Płyty wolumetryczne miały złącza po obu stronach, a połączenia przewodowe przechodziły wewnątrz pomiędzy złączami po najkrótszej ścieżce.

To był niezwykły projekt. Zmniejszyło to wielkość maszyny, a co za tym idzie, czasy przejazdu sygnałów.

Ogólnie rzecz biorąc, był to prawdopodobnie najbardziej ekstrawagancki schemat implementacji ECL z nietypowym zasilaczem ze wszystkich możliwych.

Standardowa płytka, tzw. moduł „U”, z którego zmontowano procesor (cztery asynchroniczne zatrzaski RS), wymagała aż sześciu mocy znamionowych: +40 V, +5 V, -1,6 V, -3,5 V , - 9V, -60V, nie licząc zmiennych 6V na wejście PPS, to pestka nawet jak na standardy z początku lat 1960., nie mówiąc już o 1968 czy dziś.

Technicznie logika w BESM-6 była tak naprawdę zaimplementowana na diodach, więc ostatecznie okazało się, że jest to coś pomiędzy DTL a ECL.

Osobną premią było to, że wszystko działało w powietrzu – w CDC 6600 wymagany był freon, a to było bardzo trudne i zbyt drogie.

Sam układ chłodzenia maszyny ważył ponad 7 ton i zajmował osobne pomieszczenie (wraz z jedzeniem). W BESM-6 poradzili sobie bez takich perwersji, tym bardziej, że nie wiedzieli, jak sensownie pracować z freonem w ZSRR jeszcze pod koniec lat 1980. (o tym, jak bardzo cierpieli z powodu ochłodzenia SSBIS Electronics, powiemy później).

Jak widać pomysł nie był zły, natomiast formalnie częstotliwość była taka sama jak w CDC 6600 - 10 MHz (choć to ze słów, jaka była prawdziwa i pierwsze wersje BESM-6, czysto tranzystorowy, jest nieznany).

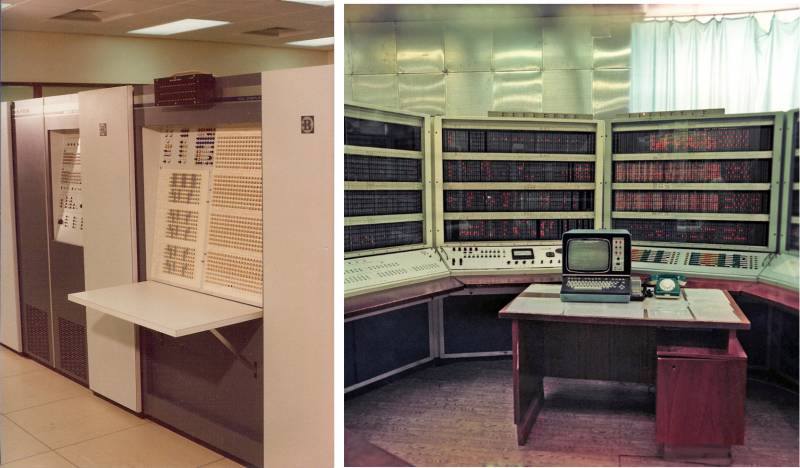

Bardzo dobrym pomysłem była też architektura systemu – w postaci podkowy, która zmniejsza długość połączeń i ułatwia zarządzanie, a BESM-6 prezentował się nie gorzej niż CDC.

Sterowanie zostało jednak zaimplementowane jak najbardziej niebanalnie – ze świętych powodów ITMiVT nie lubił konsol inżynieryjnych, tradycyjnych dla maszyn z lat 50. i 60. (a dla dużych maszyn – do lat 1970.). Z reguły wszystkie wskazania itd. były przesyłane do komputera na osobnej konsoli.

W BESM-6 tak naprawdę cały procesor był jednocześnie konsolą, kontrolki były wyświetlane na każdym TEC i energicznie mrugały podczas pracy!

Nawiasem mówiąc, konieczne jest wyjaśnienie, co to jest w ogóle.

Konsoli inżynierskiej nie należy mylić z terminalem, za terminalami pracowali programiści-użytkownicy maszyny. A konsola wyświetlała fizyczne informacje o bieżącej pracy procesora, zawartości wszystkich rejestrów itp. W większości przypadków można to zmienić ręcznie.

Takie konsole powstały nie z dobrego życia, ale dlatego, że stare maszyny wymagały debugowania i stałego monitorowania podczas wykonywania programu.

Nawiasem mówiąc, w latach 1. wielu użytkowników narzekało na brak takiego pilota w standardowej konfiguracji Elbrusa-1980.

(http://www.retrocomputingtasmania.com, https://vak.dreamwidth.org/)

Jednak wydajność maszyny nadal okazała się 2,5 razy mniejsza, a niezawodność - 1,5 razy mniejsza.

Jaki jest powód?

Częściowo rzeczywiście sowiecka baza elementów (chociaż w porównaniu z pierwszą generacją mikroukładów 155. serii w EU Row-1, radzieckie tranzystory w BESM-6 można uznać za absolutnie niezawodne).

Główny problem tkwił w architekturze systemu.

Jedyną rzeczą, w którą Lebiediew miał rękę w tej maszynie, było wymyślenie systemu dowodzenia, a okazało się, że jest tak oszukany, że, jak się później dowiadujemy, nawet dokładna implementacja BESM-6 na niewiarygodnie szybkich mikroukładach I200 ( ECL BMK) nie pozwalał nawet na 10-krotne zwiększenie wydajności (choć teoretycznie należało ją podnieść trzydzieści razy).

Nawet mikroprocesorowa implementacja monstrualnego zestawu instrukcji Lebiediewa z wczesnych lat pięćdziesiątych prawdopodobnie nie wycisnęła więcej z BESM-1950 niż obskurny procesor 6. Jednak baza elementów jest daleka od wszystkiego, architektura poleceń odgrywa dużą rolę, której szkoła Lebiediewa nigdy nie była w stanie poprawnie ocenić.

Jeśli chodzi o swojego głównego konkurenta, CDC 6600, Cray zastosował również dość egzotyczną opcję w samochodzie - bezpośrednią logikę tranzystorową (DCTL), coś pomiędzy TTL a RTL.

Bramki DCTL mają mniej komponentów, są bardziej ekonomiczne i łatwiejsze do wykonania na układach scalonych niż bramki RTL i są o rząd wielkości szybsze. Niestety DCTL ma znacznie niższy poziom sygnału, jest bardziej podatny na zakłócenia i wymaga dopasowanych charakterystyk tranzystorów, ponieważ są one mocno przeciążone. To dobra cecha, bo obniża napięcie nasycenia tranzystorów wyjściowych, ale w przypadku niedopasowanych elementów może spowolnić układ.

Działa bardzo szybko (nawet szybciej niż ECL!), natomiast nagrzewa się tak potwornie, że Cray już w 1966 roku potrzebował freonu, żeby jego samochód się nie stopił.

W przypadku DCTL różnica między poziomami logicznymi jest tak niewielka (a od tego zależy bezpośrednio szybkość przełączania), że przy sowieckiej bazie elementów układ ten w zasadzie nigdy by nie działał.

Nawet jak na standardy amerykańskie wymagane było precyzyjne dostrojenie wybranych komponentów (pierwsze kilka stron książki wydanej przez CDC na temat 6600 jest poświęconych temu, w jaki sposób nowe tranzystory krzemowe umożliwiły stworzenie tej maszyny), więc model ten nie stał się później powszechny. Ano dlatego, że nawet w wersji dyskretnej grzał się jak piekielny kocioł, w młodszych modelach - CDC 3000 i 1604 zastosowano zwykłe DTL, choć w wersji od Cray'a z kilkoma subtelnościami.

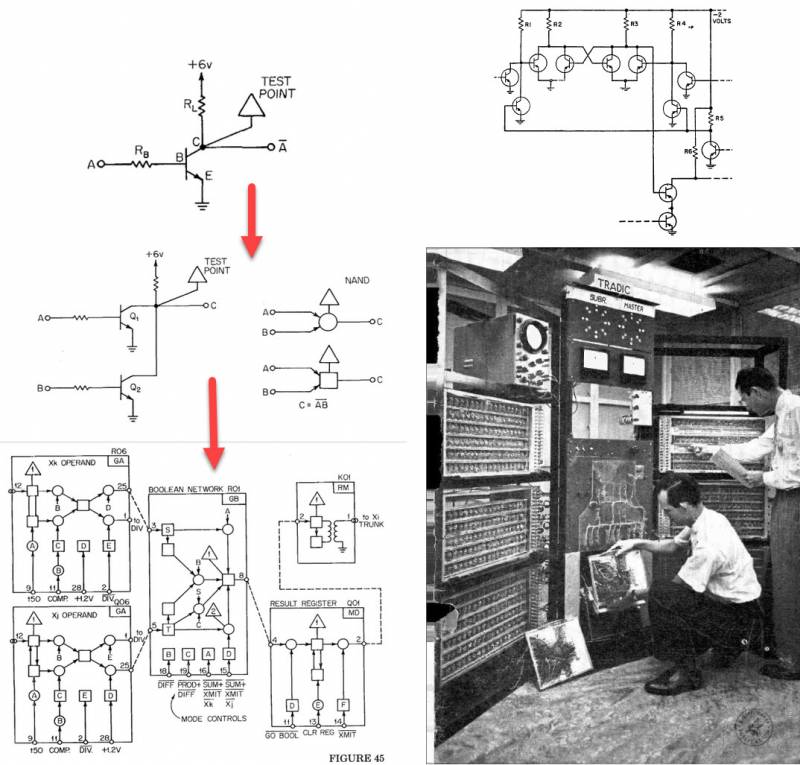

DCTL został wynaleziony w Bell Labs podczas pracy nad pierwszą w historii maszyną tranzystorową - TRADIC, ukończoną w 1954 roku. Jego wersja TRADIC Leprechaun z 1956 r. używała DCTL.

Główna idea DCTL jest prosta jak filcowy but – wyrzuć wszystkie rezystory z RTL.

Ale jak w takim razie przełączać tranzystory bez zbytniego doprowadzania ich do nasycenia?

Elementarne: zastąp rezystory tranzystorami o specjalnych impedancjach i wzmocnieniach.

Po tym następuje długa praca nad koordynacją całej tej gospodarki. W szczególności Cray obliczył, że wzmocnienie tranzystora nasyconego powinno być większe niż dwukrotność liczby obciążeń wyjściowych, a w przypadku CDC 6600 zasady są następujące: kolektor jednego tranzystora może sterować pięcioma bazami w module lub dwiema lokalnymi podstawy w module i dwie podstawy na skrętce na jednym innym module, a w module można podłączyć dokładnie sześć kolektorów.

Jak fajnie wyciśnięto z takiego schematu uczciwe 10 MHz?

Dla porównania, PDP-8, również na dyskretnych tranzystorach, wydany w 1965 roku, miał tylko 1,5 MHz, a pierwszy IBM PC, wydany 20 lat później, miał taktowanie mniej niż połowę szybkości CDC6600, mimo że był oparty na mikroprocesor. W ciągu ostatnich 20 lat wielu entuzjastów elektroniki przywróciło jako hobby montaż procesorów tranzystorowych.

Istnieją takie komputery amatorskie jak MT15, Megaprocesor czy Monster6502, ale pomimo całej bazy nowoczesnych elementów i znajomości nowych rozwiązań obwodów, które pojawiły się na przestrzeni dziesięcioleci od powstania CDC6600, żaden z nowoczesnych komputerów tranzystorowych nie osiąga nawet 1/10 prędkość wielka maszyna lat 1960-tych.

Stąd liczby 10 MHz na fundamentalnie innym obwodzie w BESM-6 wydają się wątpliwe.

Logiczna czystość CDC 6600 była również pomysłowa i minimalistyczna.

Jak w przypadku wszystkich swoich maszyn, Cray zbudował wszystko wokół jednego elementu, w tym przypadku falownika.

Dwa falowniki dają AND, jeszcze dwa + AND dają NOR, wszystko inne jest zbudowane na bazie NOR.

Interesująca jest również niezwykła notacja użyta przez Craya i odtworzona w fundamentalnej książce Design of a computer the Control Data 6600 napisanej przez Jamesa E. Thorntona, wiceprezesa CDC Advanced Design Laboratory, w 1970 roku.

Każda strzałka odpowiada inwerterowi, kółka i kwadraty wskazują, w jakiej logice należy interpretować aktualny węzeł - dodatni (kółko) lub odwrócony (kwadrat). W przypadku obu opcji schemat jest dokładnie taki sam. Każdy moduł w CDC 6600 jest zbudowany z wielu podstawowych inwerterów, każdy z jednym tranzystorem. Takie podejście było znakiem rozpoznawczym i rozpoznawalnym pomysłem Cray - weź tylko jedną z najprostszych rzeczy, zoptymalizuj do perfekcji i zbierz na niej wszystko inne.

W rezultacie CDC 6600 zdołał przetaktować do 5 ns - absolutny rekord dla maszyn opartych na dyskretnych tranzystorach, z którym nie każdy układ ECL jest w stanie pobić. „Elbrus-2” w 1989 r. miał prędkość przełączania zaworów tylko 1,5 raza mniejszą!

CDC 7600 został zbudowany w podobny sposób, tylko z całkowitą miniaturyzacją podzespołów – każdy z jego modułów składał się z 6 lub 8 płytek drukowanych połączonych drewnem kordowym z freonowym systemem chłodzenia, ale CDC 8600 (w przeciwieństwie do rowerów chodzących po Internet) powinien być już zbudowany na mikroukładach ECL.

Jedyny problem polegał na tym, że Cray nie mógł sprawić, by 4 procesory równoległe działały poprawnie, dostrojenie zajęło dużo czasu i pieniędzy (ogólnie, technologia programowania równoległego w latach 1960. nie była rozwijana tak bardzo, jak to możliwe, masowo Równolegle ILLIAC IV również nie przywodził na myśl), w wyniku czego rozczarował się konstrukcją wielu procesorów i przerzucił się na architekturę Cray-1 (a CDC na STAR-100) na architekturę wektorową.

(https://cds.cern.ch, https://vaxbarn.com, https://people.cs.clemson.edu)

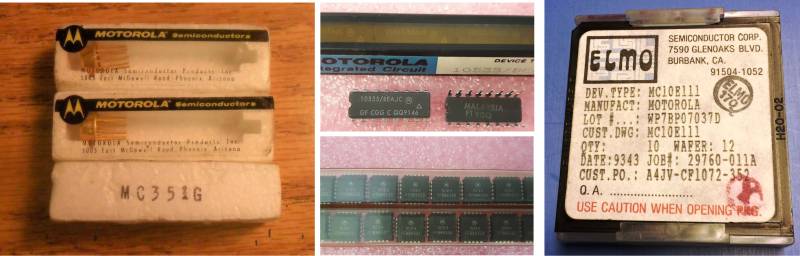

Motorola stała się ikoną ECL.

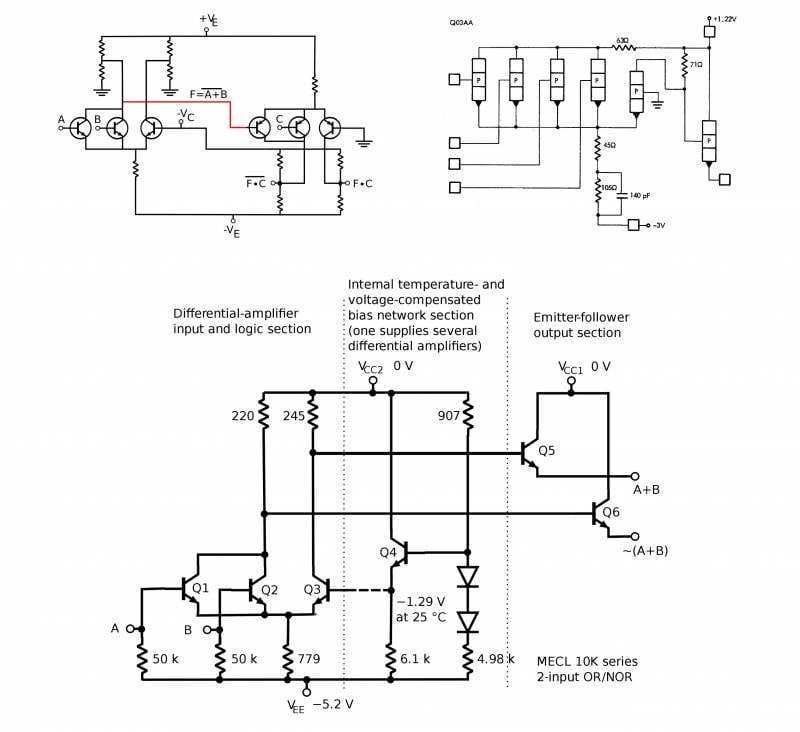

W 1962 opracowali oryginalną topologię, skromnie i po prostu nazwaną Motorola ECL (MECL).

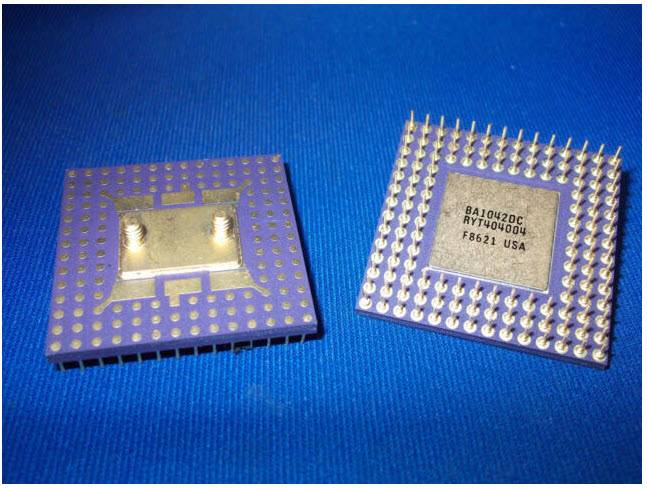

Pierwsze mikroukłady oparte na tej technologii, MC30x/MC35x, były produkowane w charakterystycznych obudowach na tablety i miały dobre parametry: opóźnienie 8–8,5 ns, częstotliwość do 30 MHz - pamiętajmy, że tranzystory mikrofalowe (no cóż, w tym czasie - mikrofale) CDC 6600 , wydany 2 lata później, wydał 10 MHz.

Druga generacja została nazwana nic dziwnego - MECL II (1966) i odpowiadała mikroukładom MC1000 / MC1200 z opóźnieniem 4 ns na bramkę.

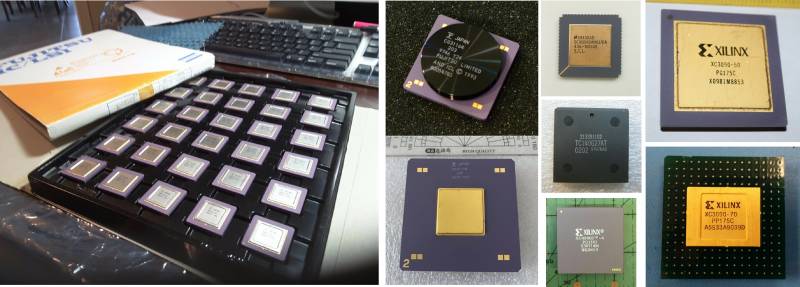

Wreszcie w 1968 roku opracowano trzecią generację logiki, która odniosła tak duży sukces, że przetrwała na linii montażowej do połowy lat 1980-tych.

MECL III odpowiadał układom z serii MC16xx, które w zależności od roku i typu pracowały na częstotliwościach od 150 MHz (MC1658 Voltage Controlled Multivibrator) do 1,2 GHz (MC1699 Divide-by-Four GHz Counter).

W wariantach z lat 1980. MECL III umożliwił zaprojektowanie chipów z maksymalnie 10 000 bramek, podkręconych do 0,1–0,2 ns.

(https://www.ebay.com)

W 1971 Motorola zdecydowała się zrobić małą gałąź swojej linii i zrobić chipy pośrednie pomiędzy i tak już nieco powolnym MC1000 a szybkim w kosmosie MC1600, chociaż do tego czasu prędkość MC1000 podwoiła się (na przykład MC1027/MC1227 120 MHz i MC1034 / MC1234 180 MHz , z czasem opóźnienia 2 ns, zamiast 4 ns dla pierwszych kopii z 1966 r.).

Tak narodziła się seria MC10000.

Różnił się od MECL III tylko wartościami rezystorów, układ był zupełnie taki sam.

Pierwsze wersje MC10k miały opóźnienia do 2-3 ns i częstotliwość do 125 MHz, a co najważniejsze, zmniejszone zużycie energii i rozpraszanie ciepła w porównaniu do MECL II/III. Jak zwykle wydano 2 serie - wojskową MC10500 (i wcześniej MC10600) oraz cywilną MC10100 (i później MC10200).

W składzie znalazło się miejsce na tak popularną wówczas rzecz jak BSP – jej rolę pełnił 4-bitowy MC10800.

Po tej linii pojawił się MC12k (1976) przy 250 MHz i MECL 10H (1981), aw 1987 r. pojawił się ECLinPS (Picosecond ECL, 0,5 ns) przy 1,1 GHz.

Motorola nie została jednak największym producentem amerykańskiej logiki ECL.

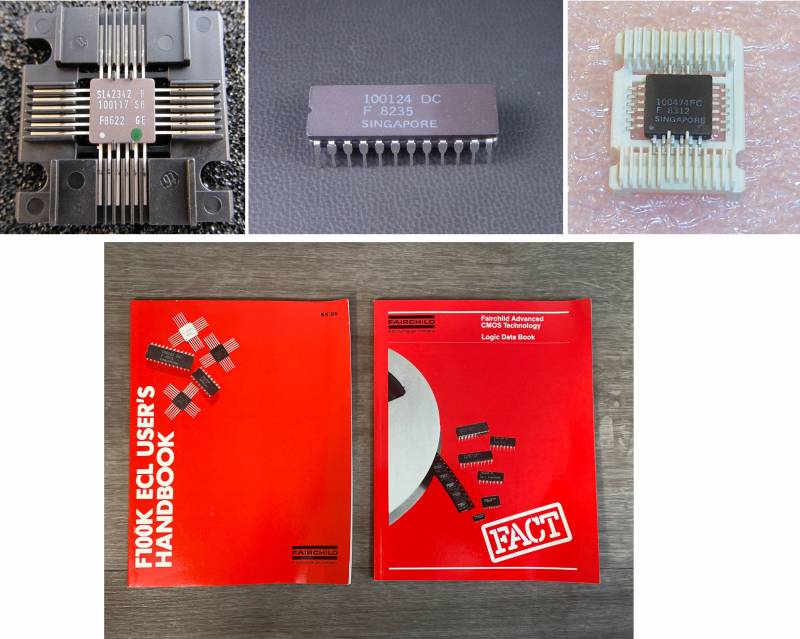

W 1973 Fairchild ogłosił modele F95K, F10K i F100K.

Linie te zadziwiają połączeniem dwóch rzeczy - jak mało o nich wiedzą (nawet w anglojęzycznym Internecie praktycznie nic nie ma, wszystko trzeba wygrzebać z książek i instrukcji) i jak świetne samochody zostały na nich zmontowane.

F10K był dalszym rozwinięciem MC10000 i znacznie się od niego różnił.

Ze względu na trudny los Fairchilda w latach 1970. (wszyscy najlepsi programiści i menedżerowie opuścili go, założywszy różnego rodzaju Signetics, Intel i AMD, a produkcja chipów była w jakiś sposób konieczna), produkcja F10K zawiesiła się na kilka lat, aż 1975.

Był to pierwszy na świecie układ ECL z pełną kompensacją napięcia i temperatury, w wyniku którego kryształ nagrzewał się znacznie bardziej równomiernie, co znacznie zmniejszyło hałas i niestabilność temperatury.

F100K był ultraszybką wersją F10K, przyspieszającą do 0,7 ns.

Wszystkie linie zostały zmontowane przy użyciu autorskiej technologii Isoplanar II, obudowy cywilne to małe DIP24. Sam F100K był serią małych luźnych elementów, jego podtypami były większe F200 (podstawowe kryształy matrycowe dla niestandardowych mikroukładów) i potężny 8-bitowy BSP F220 (pojawił się w 1980 roku, oznaczając 10022x).

(https://www.ebay.com)

Na takich chipach można było już zmontować coś naprawdę poważnego, a pojawienie się nie trwało długo - rok po wydaniu serii Seymour Cray zmontował na nim swojego świetnego Cray-1.

Cała maszyna pierwszej wersji została zaimplementowana tylko na 4 typach mikroukładów: Fairchild 11C01 (podwójny OR/NOT), Fairchild 10145A (64-bitowa pamięć RAM), Fairchild 10415 (1024-bitowa pamięć RAM) i Motorola MC10009 (tańszy odpowiednik 11C01 w schematach próbkowania adresów) ).

Co ciekawe, logika została zaimplementowana tak naprawdę na jednym typie elementów - 2OR-NOT.

Zajęło 250 000 takich mikroukładów i 65 000 mikroukładów pamięci.

Oczywiście nie tylko Cray skorzystał z radości, DEC wypuścił PDP-10 na SN74LS w 1974 roku, a rok później przeniósł starsze modele do F10K.

W 1977 roku pojawiły się ulepszone układy 4Kbit RAM, a Cray-1 doświadczył ulepszenia pamięci.

W tych samych latach Motorola ponownie licencjonowała F100K i cierpiała przez długi czas, próbując stworzyć analog, wprowadzając go dopiero w 1981 r. jako MC100k (ulepszony klon F200, zwany MCA - Macrocell Array), ale od razu wyszedł z szerszym zakresem i przyćmił oryginał (w rezultacie Cray-2 i CDC CYBER były już na nim zmontowane).

W latach 1980. na architekturze F100K wyprodukowali szereg wszelkiego rodzaju wyspecjalizowanych i po prostu potężnych maszyn, w tym tak egzotyczne, jak na przykład 64-bitowy koprocesor rzeczywisty Floating Point Systems FPS-264 (1985), który przyspieszył 5 razy w porównaniu do FPS-164 na SN74LS.

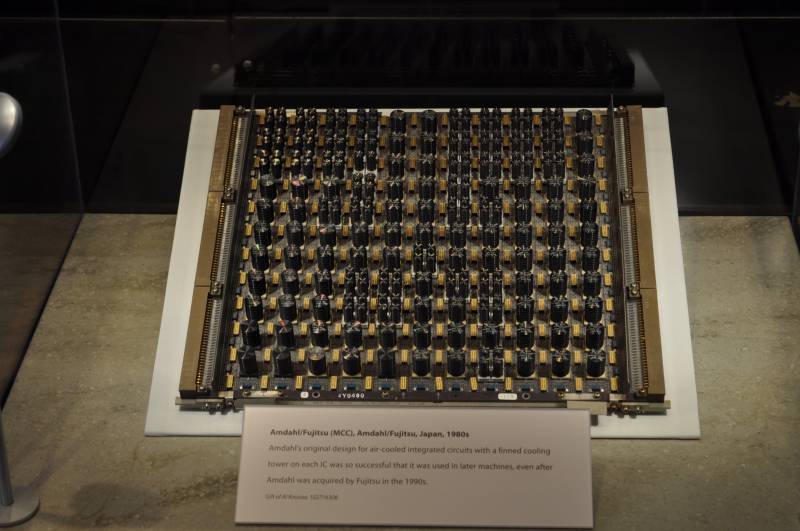

IBM rozpoczął produkcję swoich układów ECL dla S/370 pod koniec lat 1960., a Japończycy byli nie mniej znani: Fujitsu opracowało oryginalne ECL dla siebie i Amdahl (i kopiowane na licencji F100K), w Europie ECL były produkowane przez Siemensa.

(https://www.digibarn.com/ i https://www.computerhistory.org)

Główną komercyjną serią ECL-BMC z drugiej połowy lat 1980. była Motorola MCA3 ETL.

Były to potężne chipy wykonane zgodnie z zastrzeżoną technologią procesową MOSAIC III z mieszanym interfejsem, który obsługuje ECL, PECL (bardziej zaawansowana wersja logiki z dodatnim ECL-emterem z zasilaniem +5 V) i TTL. Opóźnienie nie przekraczało 150 ps, wykorzystano pełnoprawne pakiety QFP, PGA i TAB, a bramek było od 858 do 6915. Układy oznaczono po prostu zgodnie z liczbą dostępnych bramek: od MCA600ETL do MCA6500ETL .

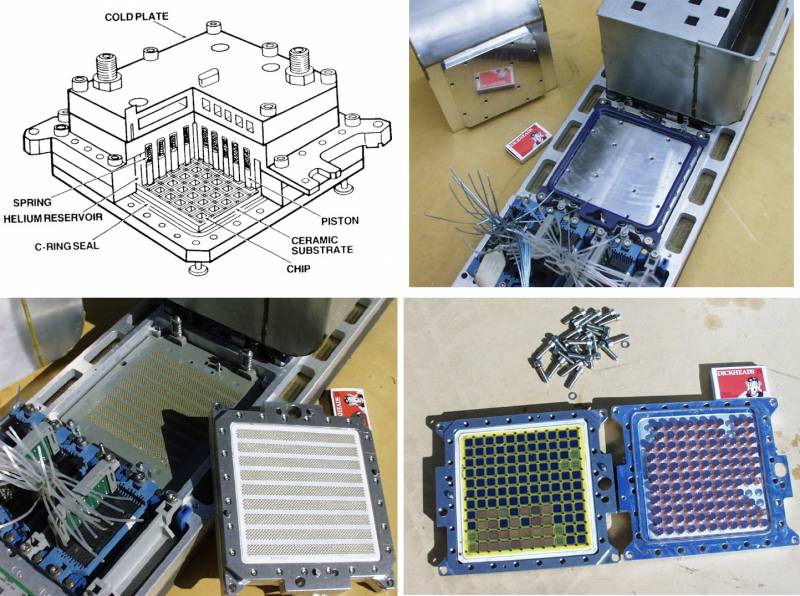

Doskonałe zużycie energii i rozpraszanie ciepła przez ECL oznaczało, że można je było stosować tylko w najwyższej klasy systemach chłodzonych cieczą, zanurzeniowo lub krio.

W zasadzie dość wolne chipy mogły żyć z powietrzem, ale w większości instalowały coś mocniejszego.

IBM ES/3900 (swoją drogą walili przez około 10 lat i tyle samo miliardów na opracowanie wielochipowego modułu TCM - Thermal Conduction Module, dla nich w rzeczywistości to właśnie wtedy procesory wielochipowe, tak popularne w naszych czasów zostały wynalezione), Amdahl 470/V6, wszystkie japońskie superkomputery lat 1980., oczywiście Cray-1 i Cray-2, starsze modele DEC od KL10 PDP-10 do VAX 9000, wszystkie wykorzystywały ECL .

Słynna seria maszyn odpornych na uszkodzenia Tandem, o której już pisaliśmy, używała SN1983AS w swoim serwerze TXP (74), ale już wzięła ECL dla swojego flagowego NonStop VLX (1986).

(https://www.researchgate.net, http://members.optusnet.com.au)

(https://i.redd.it, https://www.flickr.com/)

W 1984 roku firma DEC próbowała wypuścić „zabójcę IBM” — najpotężniejszy komputer mainframe VAX 9000.

Firma planowała zainwestować około miliarda dolarów w rozwój, pomimo znacznych obaw pracowników, że procesory RISC szybko doganiają systemy wielochipowe w BMC.

Jednak do tego czasu PDP-11 nadal mógł zmieścić się w wersji jednoukładowej (procesor J-11), klasyczny VAX już nie istniał (tylko jego wersja MicroVAX 78032).

W 1980 roku Gene Amdahl stworzył Trilogy Systems, aby ulepszyć technologię ECL w swoich komputerach typu mainframe, a firma DEC udzieliła licencji na swoje projekty.

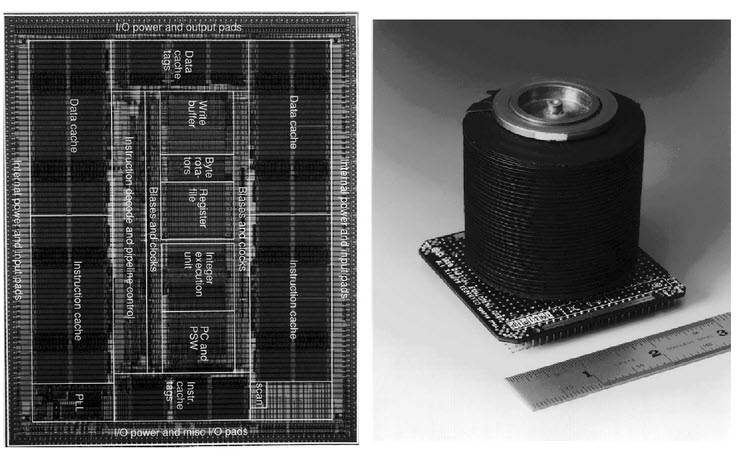

W ostatecznej wersji procesor VAX 9000 został zaimplementowany jako wielochipowy moduł typu IBM, z 13 BMC oryginalnej architektury zamówionej w Motoroli. Podczas prac rozwojowych, w 1988 roku, IBM wprowadził serwer AS/400 (który wygenerował ponad 14 miliardów dolarów sprzedaży — oni sami zarobili więcej niż cały DEC), trafiając do segmentu VAX.

W tym samym czasie firma Sun wprowadziła mikroprocesor SPARC, który pozwolił komputerom stacjonarnym przewyższyć nawet najszybsze istniejące maszyny DEC.

wykrzyknął nieszczęsny dyrektor DEC Ken Olsen, tkwiący jak radzieccy naukowcy w latach 1960. XX wieku.

Inżynierowie próbowali przekonać go do anulowania 9000, tłumacząc, że do czasu premiery nie będzie to najpotężniejszy komputer mainframe na świecie, ale zwykły serwer, tylko 1 razy droższy, ale Olsen nie ustępował, podobnie jak nasi ministrowie. i deweloperzy.

Ostatecznie DEC wpompował w projekt ponad 3,5 miliarda dolarów i zakończył go dopiero w 1990 roku, oferując maszynę porównywalną do IBM 3090 za około 4 miliony dolarów. Wyprodukowano i sprzedano tylko 40 9000 systemów - do tego czasu było oczywiste, że mikroprocesory CMOS zawładnęły tronem na zawsze.

W 1991 roku pojawił się NVAX - system dla zdrowego człowieka, opracowany przez grupę odpowiednich inżynierów DEC, o wydajności VAX 9000, ale w formacie konwencjonalnego mikroprocesora.

Pozwoliło to firmie nie umrzeć, ale stało się ostatnim w chwalebnej linii VAX - po drodze był DECchip 21064, lepiej znany jako Alpha, najmocniejszy i najlepszy procesor do początku 2000 roku.

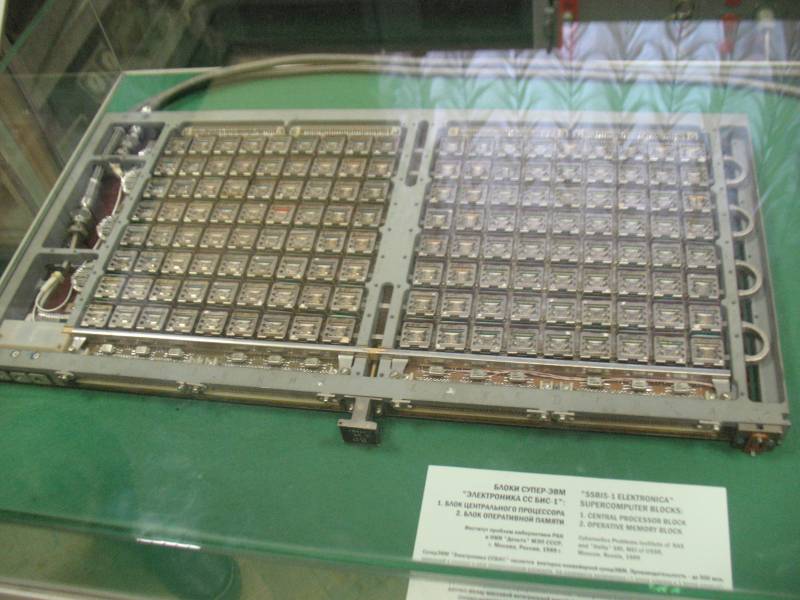

VAX 9000 stał się w pewnym sensie analogiem "Elektroniki SSBIS" - opracowanym na czystej wytrwałości i głupocie, drogim i bezużytecznym.

Jedyną różnicą było to, że ręce inżynierów DEC wyrosły z odpowiednich miejsc (a nie jak w Delta Research Institute), w efekcie samochód miał chłodzenie powietrzem, a nie freonem, był 20 razy mniejszy, tak samo szybko trwał rozwój 5 lat, a nie 10, a mimo to doszła do produkcji seryjnej.

Dla porównania: SSBIS Electronics, prototyp częściowo wprowadzony na rynek w tym samym roku, to zestaw szafek z hali montażowej zawierający 5 kilogramów złota, setki kilometrów ręcznie okablowanego kabla koncentrycznego, procesor na wielowarstwowych kanapkach płyt dyskretnych chłodzonych freonem na setkach chipów ECL, których nie dało się podkręcić nawet do paszportu 75 MHz, utknął na 66.

I tak, jeśli chodzi o wydajność, wszystko to było w przybliżeniu równe VAX 9000, a 10 lat rozwoju zostało spuchnięte, niewyobrażalna liczba milionów i wysiłki całego Instytutu Badawczego Delta, tłumy starszych akademików i mnóstwo przedsiębiorstw.

Po takiej domowej mikroelektronice chcę strzelać z litości, co ogólnie wydarzyło się w 1991 roku.

(zdjęcie z kolekcji użytkownika pixelmanca, https://www.cpu-world.com/forum/)

Zdjęcie ze zbiorów Muzeum Politechnicznego w Moskwie (https://1500py470.livejournal.com)

ECL w procesorach jest martwe na zawsze, ale jego ostatnie i najbardziej egzotyczne zastosowanie było w mikroprocesorach!

Firma Bipolar Integrated Technology, największy ekspert w dziedzinie technologii bipolarnej na początku lat 1990., postanowiła wycisnąć z niej wszystko, co możliwe i niemożliwe. Współpracowali z dwoma pionierami RISC, MIPS Computer Systems i Sun Microsystems, w celu stworzenia procesora ECL o niespotykanej mocy opartego na architekturach RISC.

Pierwsza implementacja architektury MIPS II, zestaw chipów R6000, R6010 i R6020, została wykonana jako moduł MCM i została wykorzystana w wysokowydajnych serwerach Control Data Systems InforServer z serii 4680-300 (próbowano je produkować dawna firma Control Data Corporation, zreorganizowana w 1992 r.).

Nawiasem mówiąc, podkręcili go do 80 MHz i nie przypomina to rekordów dostępnych przez ECL, ale procesor nie przepalił płyty. Dla firmy Sun powstał SPARC B5000, o którym nie ma prawie żadnych informacji.

Wreszcie, najbardziej szalonym chipem w ECL był eksperymentalny mikroprocesor firmy DEC, któremu udało się zmieścić MIPS II w jednym chipie!

W 1993 roku najpotężniejszym mikroprocesorem ogólnego przeznaczenia był Intel Pentium 66 MHz z TPD 15 watów. DEC MIPS II miał 300 MHz (!) i 115 W (!) - rozpraszanie ciepła na poziomie Core i9. Osobny artykuł został poświęcony ochłodzeniu tego potwora.

CMOS jednak podbił takie częstotliwości po 2-3 latach z rozpraszaniem ciepła 3 razy mniejszym i zapomniano o szalonym ECL.

BMK i jak go ugotować

Zanim przejdziemy do bazy elementów Elbrus-2, porozmawiajmy o tym, jak ogólnie współpracowali z BMK na Zachodzie i jakie to zwierzę.

Lata siedemdziesiąte były erą nisko- i średnio-niskich układów integracyjnych, co oznaczało, że była to jedna lub więcej płyt wysadzanych prostokątami chipów (mówimy oczywiście o poważnych procesorach maszynowych, a nie mikroprocesorach).

W 99% przypadków firmy produkujące sprzęt były zaangażowane w rozwój i produkcję procesora na wszystkich poziomach.

Wraz z początkiem lat 1980-tych nadeszła era LSI i dwóch nowych sposobów tworzenia własnej architektury.

Po pierwsze, możliwe było zmontowanie go na BSP na każdy gust, szybkość i budżet: od maleńkiego i wolnego TTL Intel 300x do potężnego 8-bitowego ECL Fairchild F220.

W tym przypadku produkcja procesora sprowadzała się w rzeczywistości do opracowania systemu poleceń i jego oprogramowania układowego w dołączonym urządzeniu sterującym.

Druga metoda przydała się, gdy architektura była zbyt potężna lub zbyt koncepcyjna, aby można ją było zaimplementować w standardowy sposób.

Producenci chipów szybko zdali sobie sprawę, że jeśli oferujesz tylko gotowe standardowe rozwiązania, możesz przegapić klientów, którzy chcą czegoś wyjątkowego za dodatkową opłatą.

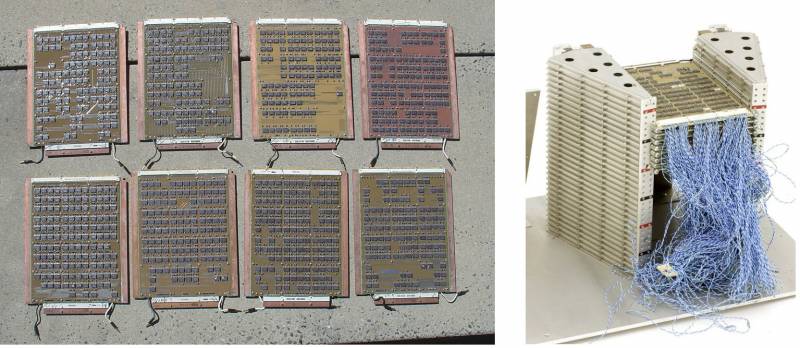

Tak narodziła się koncepcja chipów robionych na zamówienie w oparciu o to, co w ZSRR nazywano BMK, czyli podstawowe kryształy matrycowe, a na Zachodzie - Gate Array.

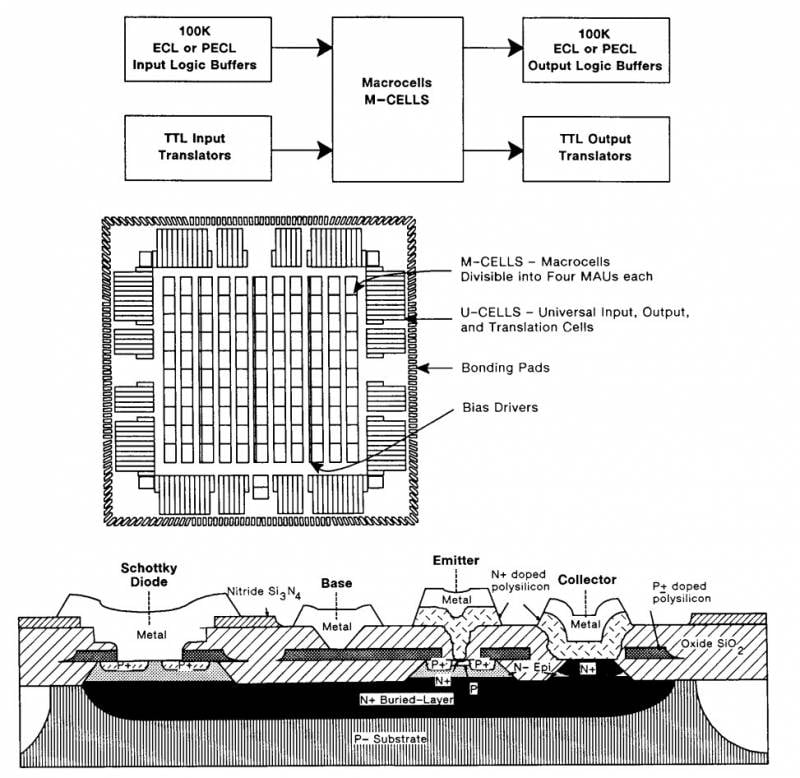

FMC jest półproduktem dla ~15-50 000 bramek, jedyną różnicą jest to, że większość tranzystorów nie ma predefiniowanej funkcji. Można je łączyć z warstwami metalizującymi, tworząc standardowe ogniwa NAND lub NOR, a następnie składać z nich w kompletny obwód z kolejną warstwą.

Czyste BMC istnieje więc tylko w broszurze reklamowej lub w magazynach wewnętrznych – wszystkie chipy, które ostatecznie opuszczają fabrykę, mają już ściśle określoną strukturę.

Płyty wzorcowe BMK z niedokończonymi chipami są zwykle wcześniej produkowane i magazynowane, w efekcie konstrukcja procesora sprowadza się do wrzucenia jego topologii do CAD, a następnie płyty trafią dalej na przenośnik, gdzie ta topologia będzie odtworzona w je, cięte, pakowane i dostarczane do klienta.

Być może ktoś słyszał o czymś podobnym i tak, teraz podobna technologia nazywa się układem scalonym specyficznym dla aplikacji (ASIC).

ASIC to już pełnoprawny SoC, zawierający z reguły I/O, kontrolery i pamięć, są one wykorzystywane w ogromnej liczbie aplikacji, obsługują wiele różnych urządzeń wbudowanych, a także np. koparki bitcoinów .

Główną różnicą jest to, że ASIC są projektowane z już uformowanych standardowych ogniw, a nie z gołych tranzystorów, jak BMC.

Oczywiście BMK były dostarczane przez całe rodziny, różniące się ilością zaworów i ceną.

W rezultacie każdy producent komputerów mógł wybrać chipset, który optymalnie pasuje do jego zestawu instrukcji.

Oczywiście istnieją subtelności, na przykład przełącznik krosowy wymaga znacznie więcej połączeń i odpowiednio warstw niż podobny układ skurczowy, podczas gdy złożoność obwodu wyłącznie pod względem liczby zaworów będzie w przybliżeniu równa.

Niewykorzystane linie i bramki zwiększają złożoność i koszt chipa, zarówno dla producenta, jak i klienta, więc wielką sztuką jest zaprojektowanie BMC w optymalny sposób, który pasuje do większości zastosowań.

W rezultacie ich twórcy starali się zapewnić taką liczbę ścieżek, która wystarczyłaby do poprowadzenia większości potencjalnie możliwej topologii na tak wielu bramkach.

Często pomaga w tym empiryczne prawo Rent, odkryte przez jednego z inżynierów IBM w 1960 r. (Rent, EF: Microminiature packaging. Logic block to pin ratio. IBM Memoranda, 28 listopada - 12 grudnia 1960). Stwierdza, że liczba pinów mikroukładu jest równa średniej liczbie połączeń na element logiczny pomnożonej przez liczbę elementów logicznych do potęgi R, gdzie R jest stałą Rent (na przykład dla mikroprocesorów R \u0,5d 0,74 - XNUMX).

Macierze bipolarne zostały wynalezione przez IBM w 1966 roku (IBM Journal of Research and Development Tom: 10, wydanie: 5, wrzesień 1966). To wtedy opisali technologię tego, co w przyszłości nazwano schematami semi-custom, a IBM nazwał technologią master slice.

Już podczas projektowania S/360 stało się jasne, że kolejna maszyna będzie musiała używać układów scalonych.

IBM nigdy niczego od nikogo nie kupił, w zasadzie wszystko dla swoich komputerów, aż do ostatniego zamka.

Oczywiście opracowali własną linię mikroukładów, które nigdy nie weszły na otwarty rynek, oraz absolutnie oryginalną technologię ich wytwarzania, aż po charakterystyczne obudowy - nie tępe DIP, ale rozpoznawalne metalowe kostki.

Ponieważ potrzebowali ogromnej liczby chipów, ich inżynierowie znaleźli sposób na radykalne obniżenie kosztów produkcji. Opracowali serię kilku matryc krzemowych ogólnego przeznaczenia, które następnie metalizowano szynami, łącząc je w wymaganej kolejności. Taki dysk nazywano mistrzowskim krojem. Już wtedy IBM używał komputerów do projektowania.

Fairchild rzucił się na ten pomysł i rok później wypuścił pierwszą na świecie komercyjną serię niestandardowych chipów Micromatrix (32-bramkową macierz DTL z opóźnieniem 20 ns). W 1968 roku wydano dwa warianty macierzy Polycell TTL (do 144 bramek, 18 ns).

Jednocześnie trzy kolejne firmy zapowiedziały takie zabawki: Sylvania SL80 (30 bramek), Motorola (25 i 80 bramek, 5 ns) oraz TI Master Slice (kilka komórek po 16 bramek).

Raytheon dołączył do uroczystości w 1971 roku, a w 1973 roku wypuścił TTL(S) RA-116, który był w produkcji do lat 80-tych.

Mniej więcej w tym czasie do biznesu BMK weszli również najwięksi producenci, tacy jak RCA i Hughes.

W 1972 roku brytyjski Ferranti wypuścił pierwszą wersję swojego ULA (Uncommited Logic Array), a później kupił nawet amerykańskiego producenta BMK Interdesign. Do 1983 roku dotarli do 10000 XNUMX bramek na torze.

CMOS otworzył najszersze możliwości produkcji niestandardowych układów scalonych, pierwsze CMOS-BMC zostały stworzone przez Roberta Lippa w 1974 roku dla International Microcircuits, Inc. (IMI).

Technologie CAD w tamtych latach były bardzo prymitywne, dlatego większość prac projektowych wykonywano ręcznie. W 1978 roku Lipp założył konkurenta IMI firmę California Devices, Inc. (CDI).

Od 1976 roku nadszedł rozkwit BMC.

Fairchild i Motorola powróciły na rynek ze swoimi ECL i Texas Instruments z I2L i STL.

W Europie co najmniej czterech producentów (Ferranti, Philips, Plessey i Siemens) było zaangażowanych w BMK, a w Japonii najbardziej znani byli Fujitsu, Hitachi i NEC.

Programowalne zworki bezpiecznikowe FPLA pojawiły się w Signetics w 1975 roku w wyniku rozwoju technologii wytwarzania zworek nichromowych stosowanych w pamięci ROM.

W tym samym okresie pojawiły się mikroprocesory i wybuchły spory o to, która opcja rozwoju zwycięży.

(https://www.ebay.com)

Przez dziesięć lat BMC uważano za poważnego konkurenta dla mikroprocesorów (prawdopodobnie montowano na nich 70 proc. dużych i średnich maszyn) i nawet nie było z góry przesądzone, które podejście wygra.

W 1979 roku firma VLSI Technology została założona, jak zwykle, przez absolwentów Fairchild Jacka Balletto, Daniela Floyda i Gunnara Wetlesena, we współpracy z Dougiem Fairbairnem z projektu Xerox PARC.

Od samego początku firma koncentrowała się na rozwoju niestandardowych chipów, opierając się na intelektualnych zasobach pobliskiego Caltech i University of Berkeley. VLSI stało się pierwszym dostawcą ASIC - niestandardowych mikroukładów opartych na standardowych ogniwach na początku lat 1980., a druga firma, LSI Logic, była liderem w produkcji mikroukładów opartych na klasycznych BMC.

Firma LSI Logic została założona w 1981 roku w tej samej słonecznej Kalifornii, a do 1985 roku wraz z Kawasaki Steel zbudowała ogromną fabrykę płyt w Tsukuba (Japonia).

W 1983 roku, na zlecenie Departamentu Obrony Stanów Zjednoczonych, opracowano specyfikację VHDL (VHSIC Hardware Description Language), zaprojektowaną do formalnego opisu obwodów logicznych na wszystkich etapach rozwoju.

W tym samym roku powstała firma Automated Integrated Design Systems, stworzona do opracowywania obwodów CAD, a także opracowano ich pierwszy produkt - analog VHDL, język Verilog.

IBM przyczynił się do wzrostu popularności rozwiązań niestandardowych, kiedy w 1981 roku wprowadził najpotężniejszy komputer mainframe nowej generacji, IBM 3081, z procesorem całkowicie złożonym z BMC ECL.

W Wielkiej Brytanii tego samego roku, na przeciwległym krańcu spektrum wydajności, Sinclair buduje ZX81 (poprzednik ikony domowego PC, ZX Spectrum) na Ferranti ULA BMK (sklonowanym w ZSRR jako T34VG1).

(http://muzeum.ipsj.or.jp)

Co więcej, rynek był nie do zatrzymania.

W 1983 roku narodziła się Altera, oferując fundamentalną nowość na rynku - rekonfigurowalny programowalny chip EP300.

W 1985 roku Ross Freeman i Bernard Vonderschmitt opracowali i opatentowali nowy sposób tworzenia takich macierzy, zwany programowalną tablicą bramek (FPGA).

Wraz z wydaniem w tym samym roku pierwszego FPGA XC2064, rozpoczyna się historia głównego konkurenta Altery, Xilinx.

Jego pierwsze produkty były pod wieloma względami podobne do wczesnych BMC - powolne i drogie, odpowiednie tylko dla niektórych niszowych rynków. Jednak prawo Moore'a szybko uczyniło z nich siłę i na początku lat 1990. poważnie zakłócili rynek chipów na zamówienie.

Wreszcie w 1988 r. założono Cadence Design Systems, firmę, która przeniosła zautomatyzowane projektowanie chipów na wyższy poziom i obecnie oferuje systemy projektowania licencjonowane za miliony dolarów.

Prawie wszystkie współczesne mikroprocesory od Intel Core i9 do Apple M1 są tworzone w Cadence CAD. Klasyczne BMC wymarły w połowie lat 1990., wyparte przez FPGA, ASIC i mikroprocesory, ale ich wpływ na rozwój komputerów był kolosalny.

Jak więc wyglądał rozwój niestandardowego układu ECL w Fairchild F200 BMK w 1981 roku?

Przejdźmy do broszury reklamowej samej firmy.

Rozwój odbywa się prawie w całości na komputerze.

Fairchild pobiera opłatę wpisową w wysokości 20 000 do 25 000 USD i zapewnia szkolenie (od 2 do 8 tygodni) w zakresie korzystania z naszej sieci komputerowej Cybernet.

Tworzenie BMC z wykorzystaniem komórek makrofunkcyjnych odbywa się ręcznie, ale kolejne kroki (generowanie wektorów testowych i weryfikacja projektu) wykorzystują program TEGAS na Cybernecie.

Łączenie i umieszczanie makr odbywa się częściowo ręcznie, częściowo za pomocą komputera; zasady projektowania są sprawdzane przez komputer.

Opłaty za czas komputera wahają się od 5 do 000 15 USD, w zależności od poziomu doświadczenia.

Wykonanie podstawowej maski dla macierzy F200 kosztuje od 10 000 do 15 000 USD; Fairchild wykona również projekt i opakowanie za dodatkowe 25 000-30 000 USD (teraz wiesz, dlaczego komputery typu mainframe są drogie).

(https://1500py470.livejournal.com)

Jak widać, zastosowanie technologii BMC wymaga znacznej inwestycji czasu i zasobów; musisz współpracować z producentem chipów, aby tworzyć diagramy logiki systemu, sekwencje testów funkcjonalnych, konwertować logikę na wzorce macierzy bramek, symulacje oprogramowania i sprzętu, diagramy połączeń, opracowywanie masek i prototypowanie.

W ZSRR wszystko to spadło na barki poszczególnych instytutów, których było trzy, a byli to konkurenci: ITMiVT (Elbrus-2 drugiej generacji), NITSEVT (ES Computer Ryad-4) i Research Institute Delta (elektronika). SSBIS).

ITMiVT i NITSEVT należały do MRP, Delta należała do MEP, a MEP posiadała 90% fabryk mikroprocesorów.

Dopóki żył przyjaciel Szokina, Kałmykow, nie stanowiło to problemu dla MCI. Wraz ze zmianą ministra na Pleszakowa w 1974 roku proces współpracy uległ spowolnieniu.

Dodatkowo sytuację pogorszyły intrygi między trzema grupami deweloperów – Przhiyalkovsky z komputerami ES i Burtsev z Elbrus-2 w MRP oraz Mielnikow z Elektroniką SSBIS z eurodeputowanego.

Poseł chciał też mieć własny superkomputer, a wyrzucając do niego Mielnikowa w 1974 roku, Burcew stworzył dla siebie niebezpiecznego konkurenta.

Na początku lat 1980. przyjęto projekt SSBIS Electronics, do którego również potrzebny był BMK, a w najbardziej krytycznym dla Elbrus-2 okresie ważyła się współpraca między MCI a europosłem.

Musiałem ukłonić się wewnętrznym konkurentom – NICEVT w ich słynnej siedzibie, 700-metrowym „leżącym wieżowcu” na Warszawskim, najdłuższym budynku naukowym na świecie. W tym wieżowcu, w sąsiednich salach, pracownicy NICEVT i ITMiVT wspólnie majstrowali przy temacie BMC.

Nic dziwnego, że rozwój BMK w Unii trwał kilka lat.

Nawet w USA, w ojczyźnie techniki, gdzie od samego początku była dokładnie badana i gdzie biznes mikroelektroniczny działał w tamtych latach po prostu na granicy ludzkiej wydajności (zważywszy na to, jakie szalone, niewyobrażalne pieniądze tam wirowały), pełna cykl projektowy BMC trwał w latach 1980-ych od 6 do 12 miesięcy.

W tym czasie tylko Japończycy prześcignęli Amerykanów, którzy pracowali już na granicy nie człowieka, a wydajności biorobotów, a więc 4 gigantów – Fujitsu, NEC, Toshiba i Hitachi (oraz Amdahl, który mądrze zamówił u Japończyków BMC z Fujitsu) rozerwał amerykański rynek na strzępy, dopóki Reagan nie zainterweniował w zakresie środków ochronnych (i dopóki IBM nieprzyjemnie pozwał Gene'a Amdala za to, że odważył się wypuścić na rynek maszynę kompatybilną z S/370, ale dwukrotnie lepszą).

Jeśli weźmiemy pod uwagę, że każdy schemat wymagał z reguły kilku iteracji w celu udoskonalenia architektury, a kosztem znikomego błędu była partia tysięcy żetonów, nie dziwi fakt, że tylko bardzo, bardzo grube firmy mogły sobie pozwolić na współpracuj z BMK przy bardzo solidnych projektach.

W rezultacie opóźnienie między ogłoszeniem nowej technologii BMK a prawdziwymi maszynami na nich wynosiło 3-4 lata, nawet w przypadku Stanów Zjednoczonych - w rzeczywistości przy całej jakości sowieckich mikroukładów to tylko cud i wyczyn, który opanowali do wydania w ciągu 6-7 lat.

Potwornie bogata firma Fujitsu, zatrudniająca tysiące inżynierów i mająca pełny cykl produkcyjny, mogła sobie pozwolić na wypuszczenie w 1980 r. komputera typu mainframe dla firmy Amdahl na BMK z zaworami 10 tys. ludzi na tiny w porównaniu do Fujitsu z zaledwie 16 matrycami zaworowymi ukończono dopiero w 1982 roku.

CDC napisało w ogłoszeniu:

Projektowanie za pomocą F200 jest bardzo kosztowne.

Rozwój odbywa się prawie w całości na komputerze wypożyczonym w Fairchild za pośrednictwem terminali klienta.

Powstaje rozsądne pytanie.

CDC i Cray były dosłownie u szczytu postępu technologicznego w latach 1980. i 1990., będąc malutkimi w stanie, zdołały przetrwać w społeczeństwie stłoczonym wokół gigantów Fujitsu, IBM i UNISYS. W tym samym czasie produkowali komputery ręcznie, a liczbę każdego modelu oszacowano na zaledwie kilkadziesiąt sztuk.

Ich interesy zawsze się toczyły, kulejąc na obie nogi, jak oni w ogóle przetrwali?

A skąd w kółko zdobywali szalone pieniądze na rozwój, zawsze schodząc do zera pod względem zysku?

I dlaczego, przy całym talencie ich inżynierów, ten program nagle przestał działać w 1990 roku?

Odpowiedź na to pytanie ma swoją nazwę.

Ronalda Wilsona Reagana.

Jak już wspomnieliśmy, lata 1970. były złotym wiekiem sowieckich partokratów.

Ciągłe odprężenie, petrodolary, współpraca techniczna ze Stanami Zjednoczonymi. Po raz pierwszy od późnych lat pięćdziesiątych naszym ludziom pozwolono ponownie korzystać z Motoroli, doszło do tego, że w latach 1950-1975 negocjacje z IBM w sprawie normalnych licencji UE były dość owocne (biorąc pod uwagę, że cały świat był już tak zajęty z tym - i Niemców, i Brytyjczyków i Japończyków), a w Motoroli legalnie kupiliśmy paczki MC1976k.

Jednak proces ciągnął się przez kilka lat, a potem nastąpiły nieprzewidziane wydarzenia, które położyły kres wszystkim planom. Afganistan, powstanie „Solidarności” w Polsce i stan wojenny w nim oraz, jak wisienka na torcie – śmierć Breżniewa i dojście do władzy „mini-Stalina” – Andropowa.

Reagan oczywiście wykorzystał to wszystko jako casus belli i nastąpiła ostatnia potężna runda zimnej wojny, która wykończyła ZSRR w 10 lat.

Rząd USA zainwestował najwięcej w ciągu dekady od II wojny światowej w różnorodne badania i rozwój podwójnego zastosowania, co doprowadziło w latach 1980. do niesamowitych zamieszek najbardziej dziwacznych, egzotycznych i unikalnych architektur i maszyn.

A od 1990 r. zniknęła potrzeba dopływu środków, a rynek pozostał, aby decydować o losie wszystkiego, co wymyślono w tłustej dekadzie.

Jak wiemy, zdecydował: w ciągu następnych 5 lat mikroprocesory RISC i ich masowo równoległa architektura wygrały konkurencję, wypierając całe cudowne zoo.

CDC otrzymało bezpośrednią inwestycję od rządu wraz z odejściem Cray'a w 1972 roku, a to pozwoliło jej na dokończenie kompletnie nieopłacalnego STAR-100, który miał ogromne trudności w projektowaniu (biorąc pod uwagę, że zaimplementowano tam jedno połączenie z komputerem sterującym PDP-11). na aż 4 typach ECL BMK po 168 zaworów).

W rzeczywistości cały projekt STAR był przykrywką dla rozwoju trzech systemów: Flexible Processor (FP), Image Processor (IP) i Advanced Flexible Processor (AFP), znany również jako Cyberplus, przeznaczony do przetwarzania obrazów fotograficznych i danych radarowych dla CIA i NSA.

Do 1986 roku zainstalowano co najmniej 21 wieloprocesorowych instalacji Cyberplus na niestandardowych chipach. Te systemy przetwarzania równoległego obejmowały od 1 do 256 procesorów Cyberplus zapewniających 250 MFLOPS każdy, które są połączone z maszynami CYBER za pośrednictwem architektury Direct Memory Attached Architecture (MIA).

Liczba wydanych i zainstalowanych FP i IP jest nieznana, ostatnim produktem wojskowym CDC jest równoległy modułowy procesor sygnałowy (PMSP) wydany w 1988 roku.

Tak więc rozwój BMC na ECL został hojnie opłacony przez rząd amerykański.

Ogólnie rzecz biorąc, w USA wydano niesamowitą liczbę tajnych architektur, głównie dla NSA i CIA, wiele kryptokomputerów wciąż jest utajnionych.

Na przykład w National Cryptologic Museum pokazano pewną płytę MC100k o nazwie CLAW 1 i mówi się, że była już zainstalowana w CDC 7600 (!), ale przede wszystkim nikt nie wie dlaczego, a jest brak informacji na ten temat.

(https://1500py470.livejournal.com, https://en.wikipedia.org)

W tym czasie w ZSRR

W ZSRR historia ECL zaczęła się, kto by w to wątpił, od tej samej Motoroli.

Czasami wspominamy, że przejście na kopiowanie serii BMK 10k, jak zwykle, zrujnowało unikalne sowieckie rozwiązania, prezentowane pod koniec lat 1960. przez serie 137, 187, 229 i 138.

Nasz ukochany Małaszewicz wspomina:

Już w 1969 roku NIIME opracowało i dostarczyło własną technologię do produkcji układów scalonych ESL w Mikron, dzięki czemu uzyskano pierwsze próbki kilku oryginalnych układów scalonych z serii 138.

Ale wkrótce rozpoczął się rozwój superkomputera Elbrus, a na prośbę jego głównego konstruktora (poparty dekretem KC KPZR i Rady Ministrów ZSRR, z którym nie można się spierać) NIIME i Micronowi powierzono reprodukcję serii Motorola MC10000.

Wyprodukowanie dwóch serii układów scalonych o podobnych właściwościach, wykraczających poza możliwości NIIME i Mikron, nie było ani celowe, ani wykonalne.

W rezultacie rozwój oryginalnej serii K138 musiał zostać zatrzymany i, aby zadowolić klienta, powstały analogi długo produkowanego MC10000 (seria 100), gorsze pod względem prędkości od serii K138 (najważniejszy parametr dla układów scalonych ESL).

W rzeczywistości tutaj, jak zwykle, wszystko jest takie, a nie takie.

Właściwie, natychmiast po założeniu w nim Zelenogradu (ponieważ uruchomiono nowe fabryki i zbudowano nowe instytuty badawcze), wprowadzono w nim coraz więcej linii kopiowania. Wraz z TTL i DTL, chipy ECL rozpoczęły się w połowie lat sześćdziesiątych.

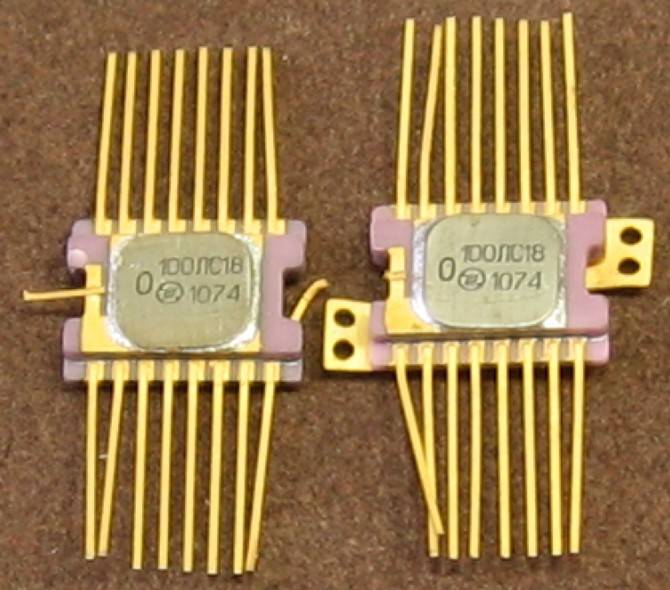

Pierwsze radzieckie ECL to rzadkie serie D34 i D35, prototyp, który pojawił się w 1968 roku i jest dokładnym klonem Motoroli MECL-I. Rok później ukazała się ich nieco ulepszona wersja - seria 137 (w płaskiej złotej kopercie dla wojska, znana jako 191).

Początkowo zostały opracowane na zlecenie Przyjałkowskiego z NICEVT do montażu okrętu flagowego pierwszego rzędu UE – EU-1050. Miał trzystopniowy asynchroniczny potok i wydajność 500 MIPS, w zasadzie nieźle.

EU-1060 miał być generalnie okrętem flagowym, ale nie zdążyli tego zrobić i przenieśli go do Ryad-2.

Zespół do opracowania maszyny R-500, która później stała się znana jako EU-1050, został utworzony w 1968 roku (początkowo chcieli wykonać 4 opcje: R-20, R-100, R-500 i R-2000 ), w tym samym roku rozpoczął się rozwój 137. serii.

Jurij Łomow, uczestnik rozwoju EU-1050, wspomina:

Nie spodziewaliśmy się więc żadnych trudności w spełnieniu wymagań wydajnościowych (500 operacji/s) z punktu widzenia możliwości architektury.

W rezultacie 137. seria była klonem MECL I z 1962 r., a 138. (z czasem opóźnienia 3 ns) była klonem MECL II.

W przypadku planarnym są to odpowiednio seria 191/197, seria 229 jest analogiem hybrydowym, a 187. to wolniejsza i zimniejsza wersja 137. Biorąc pod uwagę, że EC-1050 przekazano dopiero w 1974 r., w latach 1970-1971 nie jest faktem, że ich seryjna produkcja została w ogóle uruchomiona.

Jak widać, Borys Małaszewicz, delikatnie mówiąc, się myli, po pierwsze nie są one zbliżone do oryginalnych chipów, a po drugie ich parametry są znacznie gorsze zarówno od MECL III i MC10000, jak i Elbrus-2 (potencjalnie planowane na 1975 rok). -1978 lat) nie było sensu ich zbierać.

Trzeci błąd polega na tym, że zostały rzekomo wycofane z produkcji na zlecenie ITMiVT, a zaawansowane rozwiązania zgniły. W serii 137/138 z powodzeniem zmontowano zarówno EC-1050, jak i 1052, do 1980 roku w sumie wyprodukowano około 170 samochodów.

W zasadzie ich premiera zapewniła stabilne zamówienia na 137. serię przez kolejne 10 lat i nikt by nie pomyślał, żeby użyć jej w Elbrusie, była za wolna i nie została do tego stworzona.

Co zabawne, EC-1060 korzystał nie tylko z K500, ale także z jego oryginału - prawdziwej, żywej Motoroli MC10k! Przypomina Lomova, który był wówczas głównym twórcą ES-1060:

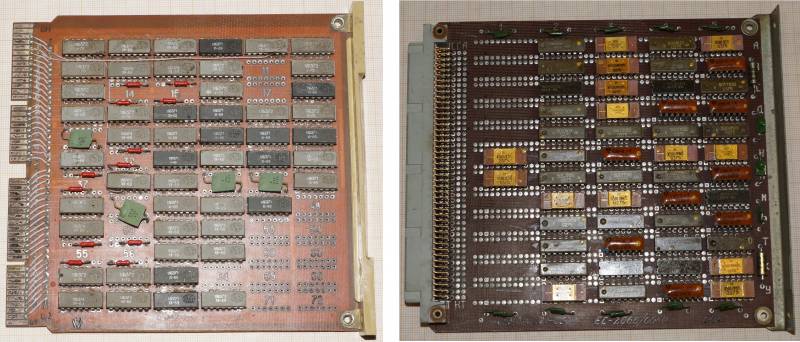

Podstawą elementów są układy scalone średniej serii K500, które zostały wygenerowane przez odpady z serii 100 i 700 stworzone dla Elbrus z ITMiVT.

Główną trudnością w rozwoju był brak w tym czasie układów scalonych pamięci statycznej dla pamięci i kanałów buforowych procesora oraz układów scalonych pamięci dynamicznej dla pamięci RAM.

Układy scalone pamięci statycznej dla prototypu i pierwszych próbek produkcyjnych trzeba było kupić za granicą.

(https://1500py470.livejournal.com)

Wielokrotnie wspominany Małaszewicz (rodowity eurodeputowany) pisze:

E. Gornev twierdzi, że kiedy K. A. Valiev był w USA (1973 lub 1974), prace nad mikroukładami ESL dopiero się rozpoczynały (od 1974) i nie było jeszcze serii 500 (a raczej K500).

Jego produkcja rozpoczęła się pod koniec lat 70-tych.

Jednak technoarcheolodzy z łatwością obalili te fantazje (od blog):

Zgodnie z ich ogólną opinią, Gorniew nie miał w tym czasie nic wspólnego z tematami ESL. Okazało się, że:

Prace nad technologią ESL w NIIME rozpoczęto nie w 1974 roku, ale znacznie wcześniej.

Już w 1969 roku uzyskano pierwsze obwody ESL (G. Krasnikov, wspomniana kolekcja „NIIME - Micron”) ...

Do czasu wizyty K. Valieva i V. Kolesnikova w USA sześć typów układów scalonych było gotowych, ich duży pakiet z układami scalonymi z serii 500 w plastikowych obudowach został pokazany w Motoroli (N. Lukanov, wspomniana kolekcja "Mikroelektronika" ).

Sam fakt tej wizyty i porównania IP potwierdza wywiad Valieva z okazji 40-lecia NIIME, w którym powiedział:

„Przywieźliśmy ze sobą próbki szybkich serii układów scalonych. A gdy Amerykanie porównali je z własnymi, okazało się, że są one prawie całkowicie wymienne. Okazuje się, że w tym czasie szliśmy, jak mówią, nozdrza w nozdrza.

W badanym okresie pracowałem w SVT, gdzie w latach 1972-1973 na bazie układów Micron ESL serii 100 opracowano wstępny projekt superkomputera 41-50, mieliśmy już próbki układów scalonych.

Z tego wynika, że informacje E. Gorneva w sprawie ESL IS są całkowicie błędne.

Nozdrza do nozdrza to oczywiście wyraźna przesada.

W rezultacie do 1975 r. Ustanowiono produkcję przemysłową 100., 500. i 700. serii, ale nie bez wielkich ościeży.

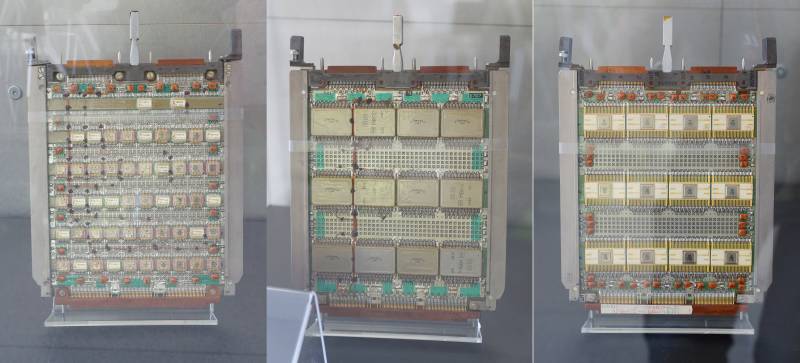

Technicznie były to te same chipy, tylko setna seria została wykonana w płaskiej wersji wojskowej, 100. - w cywilnym DIP, a 500. to specjalne zamówienie ITMiVT - bezramowe setki do umieszczenia w mikrozespołach K700, po 100–200 sztuk mikroczipy.

Zamówienie to zostało złożone w 1972 roku, ponieważ Burtsev wierzył, że użycie mikrozespołów zwiększy prędkość (pamiętajmy, że w tamtym czasie tylko IBM posiadał magię prawdziwych modułów wielochipowych).

Dlaczego K500 zostały przygotowane na wizytę Waliewa i Kolesnikowa w USA?

Nie ze względu na tajność setnej serii, ale dlatego, że w niej początkowo głupio zmieniliśmy przewody zasilające, rozkładając je po rogach obudowy.

Wydawałoby się to nonsensem?

Tak, ale nie w przypadku nanosekundowych układów scalonych.

Dzięki takiemu rozmieszczeniu zwiększyła się długość przewodników i nieznacznie zmieniła się indukcyjność, co wystarczyło, aby odporność na zakłócenia splotu była znacznie gorsza niż w oryginale, a wszyscy wiemy, jak czuły jest ECL na zakłócenia.

Pokazywanie ich byłoby tylko haniebne, ujawniając swoją ignorancję.

(https://1500py470.livejournal.com)

Co więcej, Yankees zdobył punkty za ulepszenie technologii MC10000, ponieważ pojawiła się nowa seria MC10100, a wraz z nią, jak widać na TEZ z EU-1060, proces kopiowania był trudny.

Udało im się skopiować K500TM130, ale jeszcze nie TM133, a z pamięcią MC10400 okazało się tak źle, że amerykańskie układy trzeba było instalować na seryjnych maszynach w pierwszym roku produkcji.

Amerykanie wypuścili już MC10200…

W rzeczywistości idea UE, jak już powiedzieliśmy, była dobra sama w sobie, a nasi projektanci dawali z siebie wszystko, zawiedli bazę elementów.

Seria Row-1 EU jako całość była raczej zepsuta (ze względu na słabą produkcję cywilnych TTL), ale EU-1060 początkowo okazał się tylko katastrofą.

Na przykład w tym samym instytucie badawczym „Delta” Mielnikow wolał wykonywać obliczenia dla „Elektroniki SSBIS” według klasyków - na BESM-6, dopóki ich EU-1060 nie został zastąpiony przez EU-1055M NRD, a Mielnikow ostatecznie zachował swoje nienawiść do UE na całe życie.

Poseł jednak łatwo wyszedł - wydał własne specyfikacje, które nie pokrywały się z TX w tych parametrach, których nie można było spełnić, a 500 spokojnie przeszło akceptację, korzystając z nieograniczonego patronatu lorda klonów Shokina.

Sprawa zakończyła się tym, że przedstawiciele MON (który również potrzebował potężnej UE jako komputera ogólnego przeznaczenia, a nie specjalnych komputerów obrony przeciwlotniczej/przeciwrakietowej) przyszli bezpośrednio do Shokina i wyrazili swoje oficjalne niezadowolenie z następujących faktów .

W K500, jak się okazało, w ogóle nie było obwodów kompensacji termicznej, w wyniku czego EC-1060 natychmiast nagrzewał się do 70+ stopni, a to był jedyny sposób, aby zapewnić przynajmniej pewną sprawność, ponieważ przy równomierne ogrzewanie działało (choć bezbożnie zwalniało), a gdy nie było równe, zaczęło strasznie zawodzić z powodu desynchronizacji między zimniejszymi i cieplejszymi układami scalonymi.

W rezultacie w zakresie temperatur przewidzianym w dokumentach regulujących Regionu Moskiewskiego mikroukłady nie działały, co było przedmiotem skargi.

Jednak Shokin (który wpadł w nieopisaną wściekłość, gdy myślał, że ktoś odważył się z nim nie zgodzić) pokazał, że Ministerstwo Obrony nie jest dekretem dla eurodeputowanego.

Według naocznych świadków wyjaśnił w tak potężnym chłopskim języku wielkoruskim, że eurodeputowany wyprodukował 500. serię w pełnej zgodności z jej specyfikacją, a TK z Ministerstwa Obrony można wysłać prosto i na lewo, że nawet wojsko było w szoku, i wycofali się z biura.

W rezultacie ostatecznie przeklęta seria 100/500/700 została zaakceptowana dopiero w 1980 roku i jednocześnie wyleczyła jej dziecięce rany.

Nic dziwnego, że jednym z pierwszych dekretów Gorbaczowa, którymi zaczął oczyszczać stajnie Augiasza z sowieckich ministerstw, był dekret o rezygnacji Szokina.

Nie zdążył jednak oficjalnie go wyrzucić, zdał sobie sprawę, że pachniał smażonymi i sam wolał wyjść trochę wcześniej.

Właściwie Burtsev również o tym przypomina:

Spowodowało to wiele problemów.

Układy scalone okazały się wyjątkowo zawodne: skoro zostały skopiowane, wiele nie zostało skopiowanych, były błędy systemowe.

Staliśmy cały rok, nie wiedząc, co robić, zwłaszcza z pamięcią.

Eurodeputowany zlokalizował produkcję układów scalonych w różnych fabrykach, a ja musiałem zorganizować kontrolę przychodzącą, ponieważ na przykład schematy Zelenograd (zakład Mikron) działały doskonale, a układy scalone produkowane w Kownie miały rozprężanie obudowy.

(https://1500py470.livejournal.com)

Maksymalne problemy czekały, jak można się domyślić, z K200 - próbą zobrazowania radzieckiego MCM a la IBM 3081.

Wielu inżynierów, którzy pracowali w ITMiVT, uważało decyzję Burtseva o zamieszaniu z MBIS (multichip LSI, nie mylić z dalszym MAIS - matrix LSI, czyli BMK serii I200!) za całkowicie błędną i dodatkowo opóźnioną pracę nad Elbrus-2.

Pierwsze K200 były gotowe w 1976 roku i rozpoczął się rozwój procesora.

Około połowa jego logiki została zaimplementowana jako pojedyncze układy z serii 100, a druga połowa jako moduły K200.

Instalacja pakowania została wykonana w samym ITMiVT i byłoby lepiej, gdyby tego nie zrobili...

Debugowanie rozpoczęło się dopiero w 1981 roku, według jednego z szacunków niezawodność zespołów była taka, że przy każdym włączaniu i wyłączaniu procesora coś się paliło.

Codziennie wymieniano do 5 stref TEZ, z tego powodu debugowanie trwało trzy razy dłużej niż planowano.

Generalnie z TTL w Elbrusie-1 sytuacja nie była dużo lepsza.

W efekcie do 1984 r. samochód został de jure przekazany de iure, de facto był to prototyp, który jeszcze nie został wypolerowany i wypolerowany (jak wiemy, wypolerowano go dopiero do 1989 r., po raz kolejny zmieniając bazę elementów, oraz wszedł do pełnoprawnej serii dopiero od 1990 r.).

W rezultacie Burcew przez 10 lat nie dotrzymał wszelkich możliwych terminów (pomimo faktu, że ersatz-Elbrus, pierwsza wersja na TTL, również działała normalnie nie wcześniej niż na początku lat 1980. i dla tak dzikiego napływu pieniędzy i napięcia siła okazała się dość nieszczęśliwa).

To właśnie pozwoliło nieszczęśnikom Burcewa dokonać rewolucji w ITMiVT i korzystając z faktu, że jego potężny patron Kałmykow leżał w grobie przez 10 lat, powtórzyć nad nim to samo, co Burcew zrobił ze Starosem.

Jeszcze przed dostarczeniem Elbrusa-2 stało się jasne, że podobnie jak pierwsza wersja jest beznadziejnie przestarzała technicznie.

Seria MC10k wyglądała dobrze w 1970 roku, ale już w 1985 roku była to już muzealny złom.

Jak już wspomnieliśmy, w ZSRR było wystarczająco dużo kandydatów na nowe technologie.

Instytut Badawczy Delta – od strony MEP i ITMiVT z NICEVT – od strony MRP, natomiast w pierwszym etapie wszystkie typy ECL były produkowane i rozwijane tylko w Zelenogradzie w zakładach MEP.

informacja