Narodziny sowieckiego systemu obrony przeciwrakietowej. Bitwa sowieckich ministerstw o mikroukłady

Ostre zainteresowanie zwiększeniem poziomu integracji początkowo wyszło nie od twórców Elbrus-2, ale od Przyjalkovsky'ego z NICEVT.

Faktem było, że, jak już powiedzieliśmy, w połowie lat 1970. nastąpił prawdziwy renesans ECL BMK. Prawie wszystkie klony IBM S/370 - Siemens, Fujitsu, Amdahl - zostały przeniesione na układy niestandardowe.

Jednym z głównych i, jakkolwiek by to nie powiedzieć, dobrych celów tworzenia komputerów w UE było ciągłe utrzymywanie parytetu komputerów krajowych z rozwiązaniami zachodnimi.

Oczywiście nadchodzący Ryad-3 musiał być montowany na tej samej podstawie elementów, aby nadążyć za pokoleniem. Przyjalkovsky bardzo dobrze to rozumiał i rozpoczął wojnę z eurodeputowanym o zdobycie nowych mikroukładów (Burcew podciągnął się później).

Problem polegał na tym, że eurodeputowany, który był dręczony krwawym potem z serią 100/500/700, absolutnie nie był chętny, aby dostać się do butelki i rozpocząć nowy rozwój, o rząd wielkości trudniejszy niż wszystko, co robili, mając nawet nie dokończył zdzierstwa poprzedniej generacji.

Jak pamiętamy, połowa lat siedemdziesiątych była szczytem bierności Breżniewa, kiedy ministrowie woleli dzielić się zyskownymi i bezproblemowymi kontraktami, niż zajmować się dodatkowym bólem głowy.

Jeśli możliwości wykorzystania pamięci LSI były oczywiste, to przeniesienie struktur logicznych komputera do LIS spowodowało pewien podział wśród programistów.

Przez długi czas przedsiębiorstwa z branży elektronicznej sprzeciwiały się produkcji matrycy typu LSI. W warunkach istniejącego mechanizmu ekonomicznego opanowanie kilkuset typów LSI przy stosunkowo niewielkiej produkcji seryjnej każdego typu było dla nich niezwykle nieopłacalne.

Jako alternatywę zaproponowano projekt stworzenia komputera na jednym lub kilku typach mikroprocesorów, mikroprogramowanych do wykonywania funkcji każdego obwodu logicznego i każdego węzła dużego komputera.

W tych okolicznościach, przy niechęci przemysłu elektronicznego do produkcji matrycowego LSI i niemożności zachowania kompatybilności nie tylko z IBM, ale także z ES EVM-2 przy poważnej ingerencji w sprawdzone obwody z mikroprocesorami, podjęto wymuszoną decyzję podzielić ES EVM-3 na dwa etapy.

Pierwszy etap komputerów domowych - ES-1036, 1046 i 1066 - do zbudowania na najnowszych mikroukładach o średnim stopniu integracji serii IS-500, a drugi - ES-1037,1047 i 1067 - do realizacji na macierzy LSI, które powinny się pojawić przed rozpoczęciem projektowania.

Oczywiście spowodowało to opóźnienie technologiczne w stosunku do zachodnich komputerów, co nie mogło nie doprowadzić do opóźnienia w architekturze, ale w latach 1977–1978 było inne wyjście. nie miał.

pisał Przyjałkowski.

Co dziwne, pomogło to w tej samej przeklętej wojnie afgańskiej i przybyciu Reagana.

Senny sen został nagle otrząsnięty, ZSRR ponownie znalazł się w kręgu wrogów, Reagan żartował na żywo na antenie:

Ogólnie chwalebne czasy maniaków Lemay i MacArthur praktycznie powróciły.

Przerażony ZSRR nie mógł sobie przypomnieć, jak w ogóle realizowane są wielkie projekty infrastrukturalne.

Oczywiście musieliśmy też zapomnieć o współpracy z Motorolą, koniec z MC10100 w komputerach ES.

IEP przyspiesza

W 1979 roku eurodeputowany pilnie zaczął kopiować F100K i ich BMK F200, ale oficjalny rozkaz publiczny dla BMK na 1000 zaworów został sformułowany nieco później, po artykule programowym Przhiyalkovsky'ego, Lomova i Faizulaeva „Problemy i sposoby technicznej realizacji wysokowydajne komputery oparte na LSI”, opublikowanej w USiM nr 6 w 1980 roku.

W rezultacie temat Irbis, klonowanie BMK, znalazł się w planie pięcioletniego planu XI z lat 1981–1985, stąd wskaźniki mikroukładowe: I200 (na cześć F200), I300 (na cześć F300), a następnie chcieli osiągnąć własne I400 i I500 (przyjmowanie za podstawę nie jest już Fairchildem).

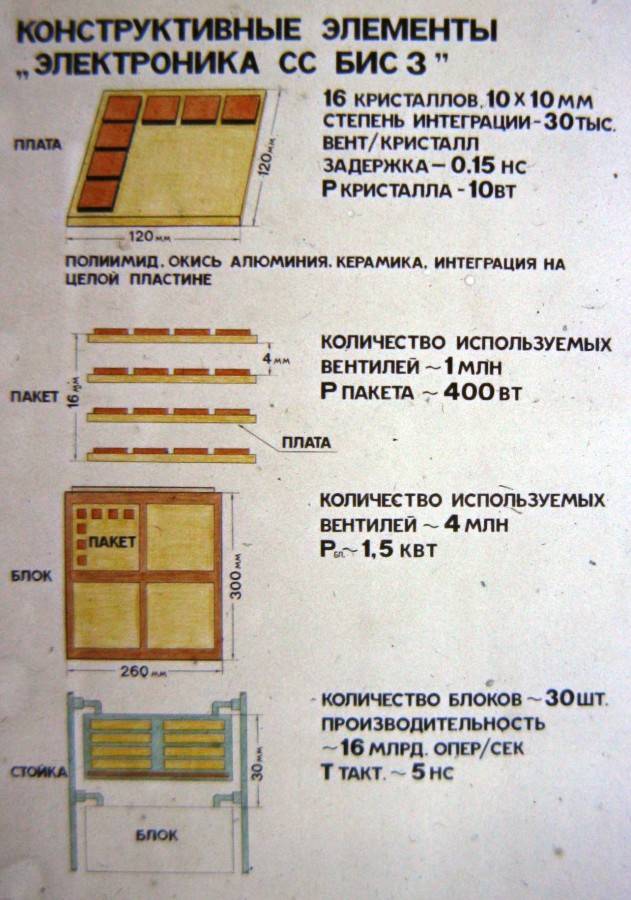

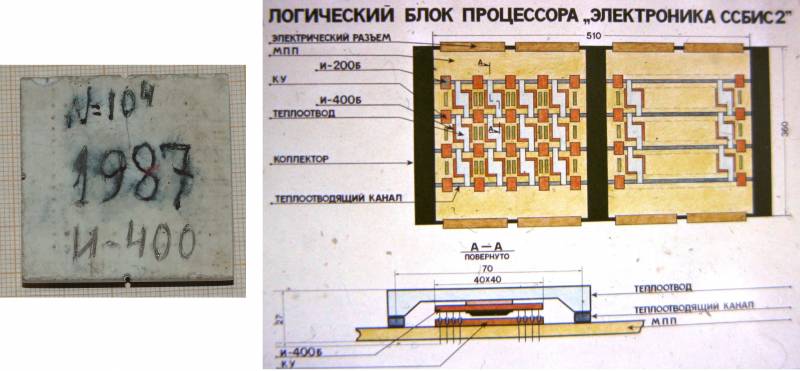

Jednocześnie eurodeputowany zdecydował, na fali tak zwanego szumu wokół drugiej rundy zimnej wojny, poruszyć temat własnego superkomputera i rozpocząć rozwój „Elektroniki SSBIS” i to z całej rosyjskiej duszy - rodzina trzech maszyn jednocześnie.

W tym samym momencie światło ujrzał także Burcew i zdał sobie sprawę, że ciąg lukratywnych zamówień ma przekazać ITMiVT bezpośrednio do NICEVT (a w Rjadzie-4 Przhiyalkovsky zapewnił już prawdziwe superkomputery, a ponadto aktywnie rozważali temat potężnej matrycy). dla nich koprocesory wektorowe) oraz Instytut Badawczy „Delta”.

Pomimo tego, że Elbrus-2 na 100. serii właśnie zaczął być debugowany, ostro wpisuje swój zespół na listę zamówień na 1520. serię i jednocześnie zachęca Sokołowa do rozpoczęcia prac nad koprocesorem wektorowym dla wciąż nie gotowych Elbrus, żeby nie okazał się gorszy od europosła.

Ponadto w połowie lat 1980. miał też pomysł na własną linię superkomputerów typu Elbrus.

W rezultacie do 1985 r. napięty ZSRR ciągnął na swój garb jednocześnie trzy równoległe linie superkomputerów - potencjalną serię Elbrus (planowano 3 maszyny), potencjalną serię Elbrus (planowano 3–5 maszyn) i potencjalną serię EU Row 4 serii (2–3 maszyny plus projekty koprocesorowe dla nich, ponadto nadzorowali również całkowicie lewicowe opracowania architektoniczne, takie jak makro-rurociąg Głuszkowa, który również otrzymał indeks UE).

Wszyscy zaciekle konkurują o finanse, fabryki i zasoby intelektualne deweloperów.

Z całej wspaniałości tylko druga wersja Elbrus-2 zdołała zakończyć produkcję na małą skalę.

"Elektronika SSBIS" (prawdopodobnie) została wykonana w 4 egzemplarzach, ale żaden z nich nie został zainstalowany i uruchomiony, po 1991 wszystkie maszyny zostały przekazane za złoto.

Superkomputery rzędu 4 nie zostały w ogóle ukończone.

Jak już powiedzieliśmy, uruchomiono dwa projekty - 1500. serię (dla F100) i Irbis dla F200.

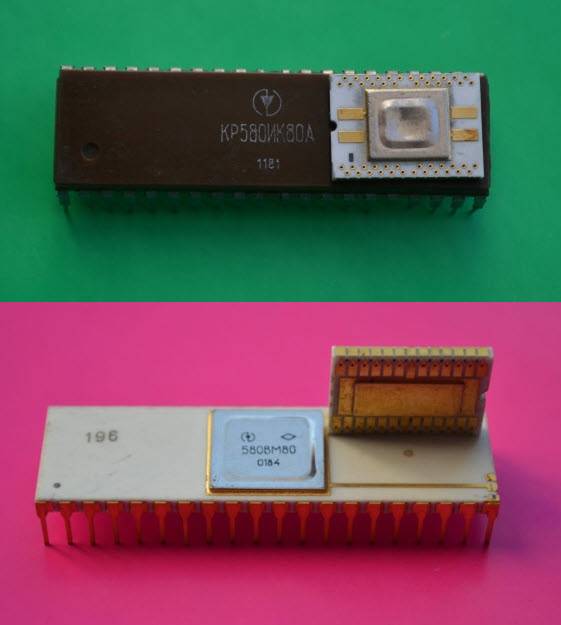

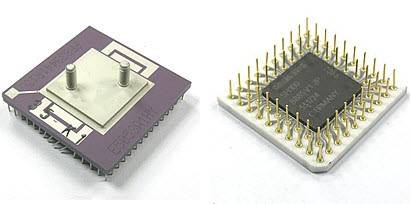

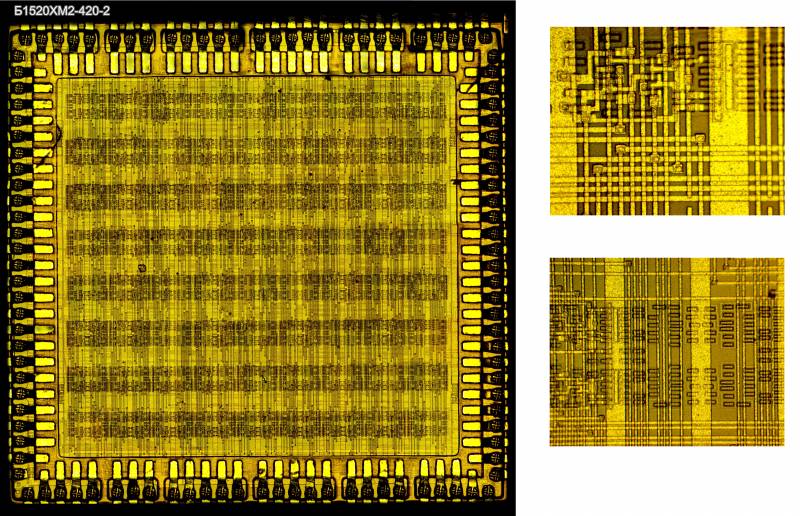

Mikroukłady „Irbis” otrzymały oznaczenie K (N) 152x (N - w zależności od rodzaju obudowy) i wersję XM1-XM6.

Kryształy wewnątrz tych mikroukładów zostały oznaczone jako I200 - I500 różnymi literami, na przykład dodanie „B” oznaczało zmianę technologii procesu z 2,5 mikrona na 1,5 mikrona.

Seria 1500 została zaprojektowana głównie w celu zastąpienia importu w starszych modelach EC Ryad-3 i zastosowania w różnych komputerach pokładowych i była kompletnym zestawem różnych proszków sypkich typu 2I-NE itp.

Ta seria, nowsza w porównaniu do 100/500/700, została wykorzystana do początkowego rozwoju „Electronics SSBIS” i EU Row-4.

Ale z 1520. serią wszystko było bardzo, bardzo interesujące, do tego stopnia, że najlepsi technoarcheolodzy spędzili kilka lat na badaniach, aby zrozumieć, co i jak tam zostało wyprodukowane.

Krótka wersja wydarzeń jest następująca.

I200 zaczął być rozwijany przy pełnej i szczerej zgodzie MEP i MRP, przede wszystkim dla Elbrus-2, a kryształy z tej serii stały się jedynymi, które zostały całkowicie wykończone i zdebugowane i użyte w naprawdę działającej maszynie, która była z nimi na płytach do produkcja seryjna.

Proces trwał kilka lat, od początku lat 1980. do 1985-1986, a żyjąca na nich maszyna była gotowa około 1987 roku.

Dokończenie Elbrus-2 było konieczne za wszelką cenę: zarówno eurodeputowany, jak i MRP rozumieli to i współpracowali.

W 1981 roku ukazała się seria Fairchild F300 BMK, która jest ośmiokrotnie bardziej skomplikowana niż F200 i ma trzy poziomy zużycia energii: 8, 4 i 2 W, przy prędkości 0,4 ns. Została natychmiast przyjęta do rozwoju jako I300.

Tutaj, na szczęście, eurodeputowany wymyślił już serię trzech „elektronicznych SSBIS”, a Burtsev został przeniesiony do wektora MCP. W związku z takim konfliktem interesów zakład Mikron MEP zaczął coraz częściej wysyłać przedstawicieli ITMiVT i NITSEVT na piesze wycieczki, więc wszystko musieli robić sami.

W rezultacie opracowali różne wersje chipów na I300 równolegle i niezależnie.

Obie opcje zostały wprowadzone do serii i zostały wykorzystane do montażu elektroniki SSBIS (wersja ostateczna), MCP Burtseva i Elbrus-3 Babayan, ale żadna z tych maszyn naprawdę nie działała.

Co więcej, zespół MEP pozostał do cięcia projektu I400 dla nadchodzącej, ich zdaniem, „Electronics SSBIS-2” (chcieli wprowadzić go do 1989 roku, bardzo optymistycznie, biorąc pod uwagę, że do tego czasu ledwo ukończyli pierwszą wersję ), losy I500 są nadal owiane ciemnością, ale był to już początek lat 1990., kiedy skończyła się sowiecka mikroelektronika.

Zabawnie można zauważyć, że początkowa wydajność serii I200/I300 (klony zaczęły powstawać niemal wcześniej niż ich prototyp F200/F300 oficjalnie pojawił się na rynku cywilnym w Stanach Zjednoczonych) nie ma związku z tematem Elbrusa na wszyscy, ale technoarcheolodzy są tu jak woda w ustach:

<…>

Jest bardzo prawdopodobne, że nasz projekt wraz z rozwojem Elektronika SS BIS mógłby być ekranem do rozwoju i produkcji zupełnie innej maszyny, maszyn lub różnych urządzeń specjalnych, o których wciąż nie można mówić i pisać…

Więcej niż te cytaty o potencjalnych alternatywnych zastosowaniach I200 nie wiadomo (chociaż, jak pamiętamy, w USA równolegle z projektem CDC STAR powstało również wiele ciekawych rzeczy).

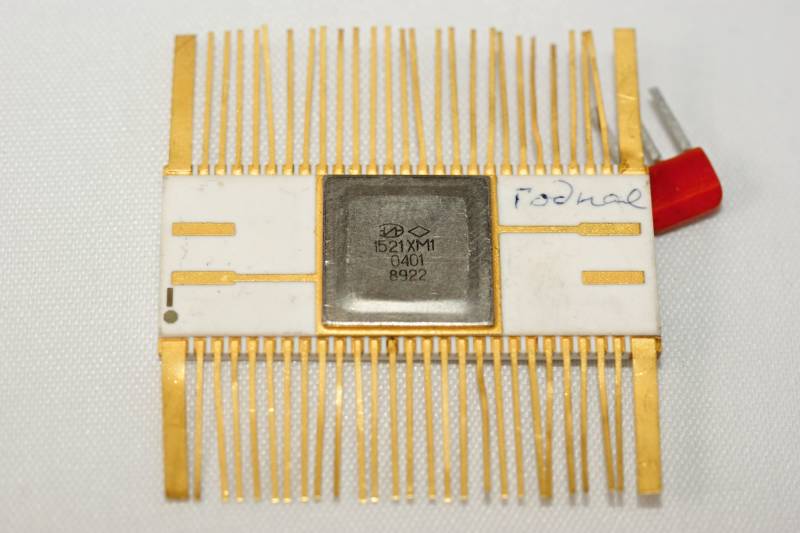

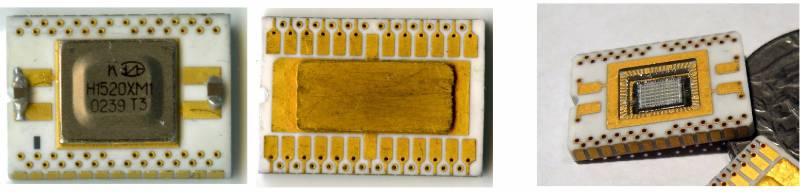

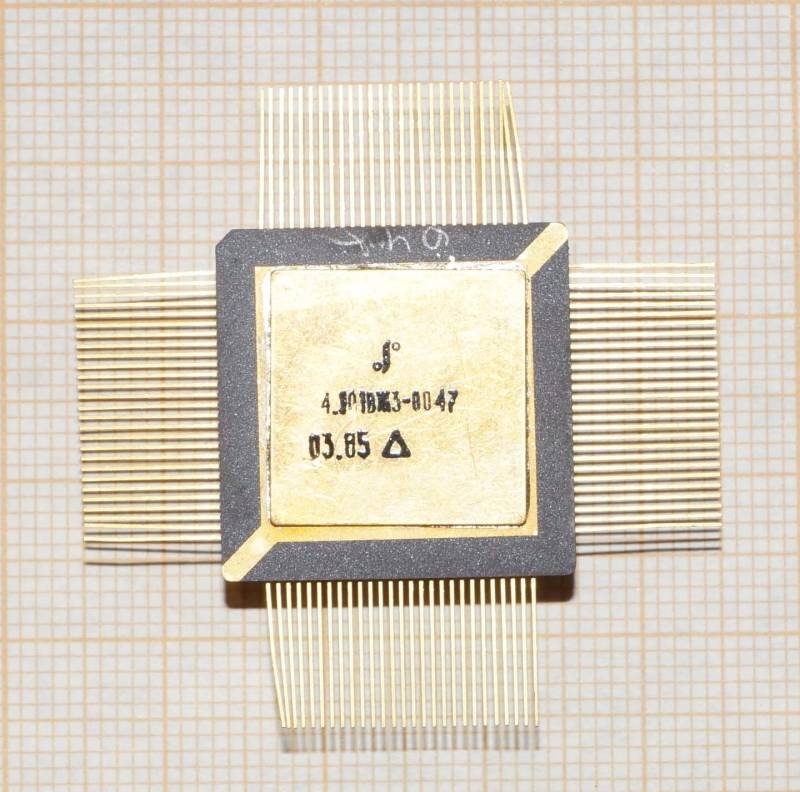

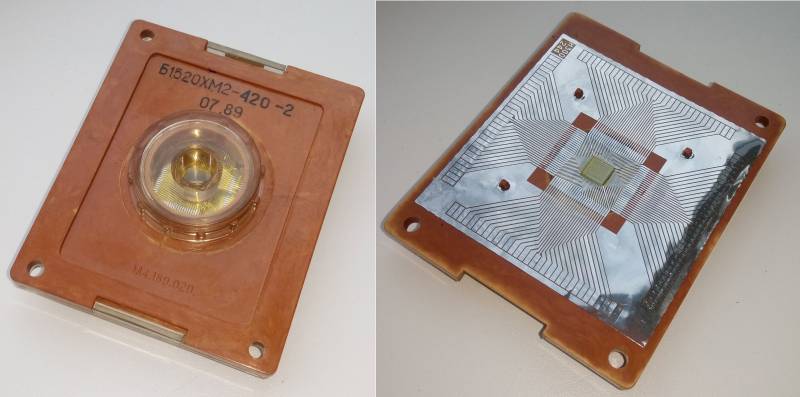

Tak czy inaczej, niezawodnie wiadomo, że w ostatecznej wersji Elbrus-2 zastosowano KN1520XM1 na krysztale I200M 2,5 mikrona, kompatybilnym z serią 100/500/700.

Początkowo opracowano KN1521XM1 (I200), kompatybilny z serią 1500, ale nie pasował do Elbrus-2, ponieważ ogniwa peryferyjne nie mogły być kompatybilne jednocześnie z serią 100 i 1500.

W elementach wewnętrznych 1521XM1 źródła prądu (zarówno w wyłącznikach prądowych, jak i w wtórnikach emiterowych) są na rezystorach, co oznacza, że gdy zmienia się moc znamionowa, należy również zmienić moc rezystora, a moc tam była inna: 4,5 V i 5,2 V.

Ponadto serie 100 i 1500 miały różne poziomy logiczne i różne zachowanie tych poziomów przy zmianie temperatury i napięcia zasilania. Wariant kryształu w technologii procesu 1,5 mikrona zamiast 2,5 mikrona nazwano I200B, a jego mikroukład to KN1520XM4. Na tym zmontowali ostateczną wersję „Electronics SSBIS”.

Według wspomnień inżynierów Elbrus-2:

Wydajność jest około 2 razy szybsza.

Wyjątkiem jest pamięć.

1521 nie miał pamięci na chipie, tylko logikę, więc bezpośrednia wymiana na K200 z pamięcią podręczną była niemożliwa.

Karty pamięci podręcznej zostały przeprojektowane, każdy mikrozespół z 8 układami 700RU148 (64 bity) został zastąpiony dwoma układami 100RU410A (256 bitów), natomiast nowa płyta (zwykła, bez mikrozespołów) stała się w połowie pusta, dużo wolnych miejsc.

Niemniej jednak te płyty (obie ciasno upakowane, wszystkie miejsca po obu stronach są zajęte na K200, a do połowy puste na 100RU410A) były dokładnymi analogami funkcjonalnymi, jeden został zastąpiony innym, często w jednym procesorze były TEC obu odmian.

100RU410A został wydany później niż 100RU148, więc niemożliwe było natychmiastowe wykonanie go na 100RU410A.

Powstawały od około 1985 roku, kiedy Elbrus-2 był testowany w 1984 roku. Jeszcze ich tam nie było.

Każdy HM1 był ogrzewany mocą 4 W, w wyniku czego z jednego TEC musiało usunąć ponad 0,5 kW.

Elbrus-2 poradził sobie z chłodzeniem wodnym na mieszance wody i alkoholu (jak MCP), ale monstrualna i 2 razy potężniejsza Elektronika SSBIS wymagała freonu.

Była to jedyna maszyna w ZSRR z chłodzeniem kriogenicznym (chociaż znowu pojawiły się pogłoski o niektórych ściśle tajnych projektach z chłodzeniem zmiennofazowym - odparowywaniem azotu) i wystarczająco ucierpieli na tym.

Rozwój BMK dla Elbrus-2 został zakończony w latach 1983-1984, a pierwszy procesor został na nich zmontowany w 1986 roku, ale nie działał.

Posełowi zajęło jeszcze kilka lat opanowanie produkcji I200 na odpowiednim poziomie i tyle samo lat ITMiVT na stworzenie dla nich odpowiednich TEZ.

Pierwsze wersje „Elbrusa” w BMK nie działały, ponieważ akademicy schrzanili system chłodzenia, nie było wśród nich specjalistów od poziomu Craya.

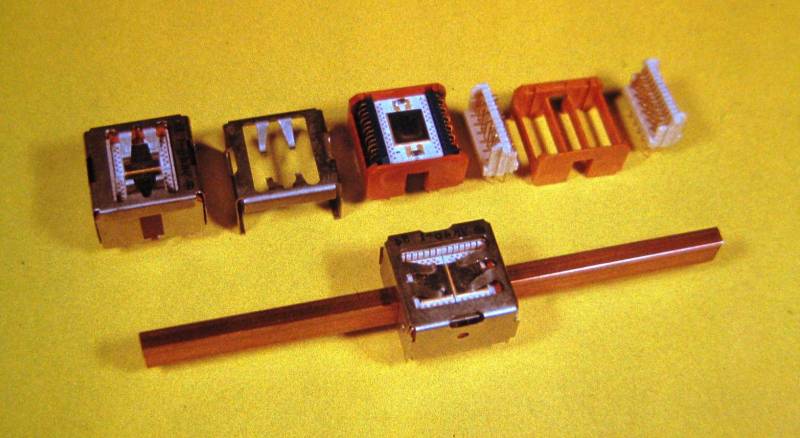

Pierwsze ceramiczne obudowy XM1 po prostu pękały w wyniku nagrzewania, ponieważ zamontowane chłodzenie było niewystarczające.

Był też problem z kadłubami, pierwsze partie trzeba było kupić w Japonii, ponieważ zakład w Yoshkar-Ola miał wiele trudności z ich rozwojem.

Tak czy inaczej, pierwszy w 100% sprawny Elbrus-2 drugiej generacji został wprowadzony dopiero w 1989 roku.

Problem dotyczył nie tylko obudów, do produkcji działających układów scalonych z półfabrykatów-BMC potrzebne są odpowiednie systemy CAD, wykonanie tego ręcznie jest całkowicie niewdzięcznym zadaniem.

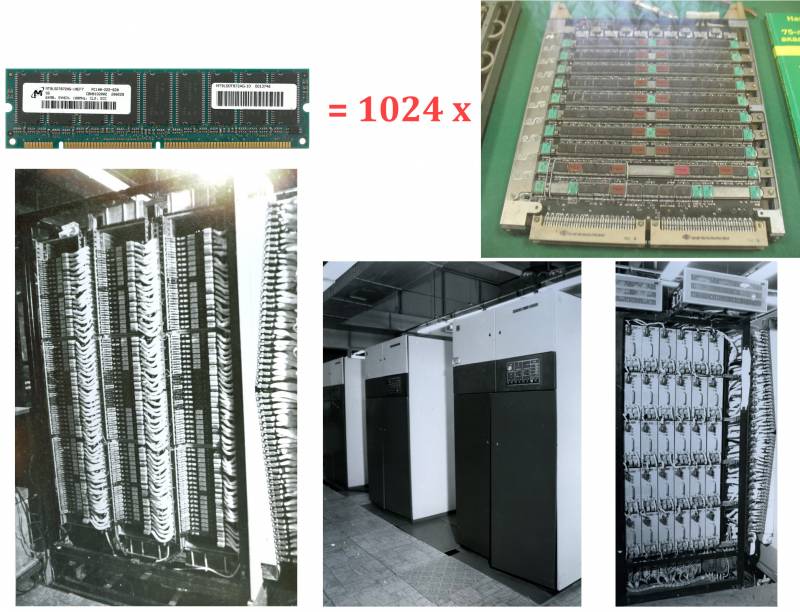

Powinniśmy również powiedzieć kilka słów o sowieckich układach RAM do systemów o wysokiej wydajności.

Pamięć w superkomputerze jest trzecią najważniejszą rzeczą, po procesorze i układzie chłodzenia (a kompetentny projekt chłodzenia generalnie jest na pierwszym miejscu, co nasi zagorzali teoretycy, przyzwyczajeni do opracowywania komputerów poprzez rysowanie wielokolorowych kwadratów, „i oto jesteśmy potężny super-mega procesor).

Kiedy latem 1980 roku pierwszy TOR został zatwierdzony do prac badawczych nad SSBIS, nasza skupiła się na Cyber 203 i CRAY-1. Pamięć 1 megasłowa wydawała się całkiem przyzwoita i wszyscy spodziewali się, że w efekcie konieczne będzie wykonanie RAM z czasem dostępu 60–80 ns, 64 bity plus kontrola, wystarczającym do korygowania pojedynczych błędów i wykrywania podwójnych.

Zadanie rozpoczęcia kopiowania serii F100K zostało wysłane do trzech organizacji, NIIME, Integral i Svetlana, w lutym 1980 roku z wymogiem wykonania nie później niż w grudniu 1981 roku.

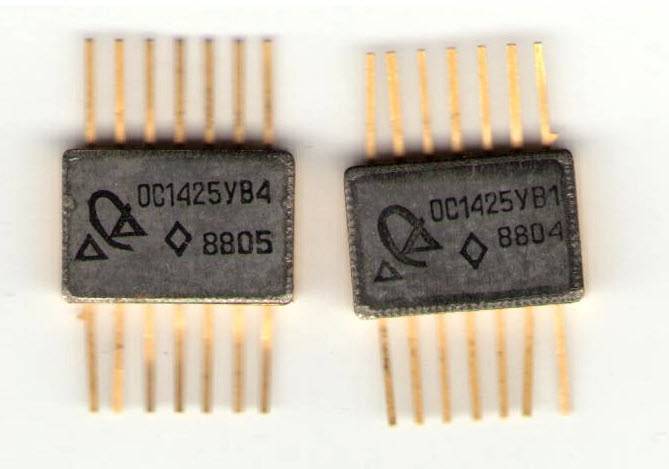

Ze względu na wagę zadania pierwszy mikroukład z serii, K1500RU415, był jednocześnie objęty przez NIIME i Integral. W tym samym czasie, równolegle z zakładem w Yoshkar-Ola, poinstruowano ich, aby opracować walizkę flatpack-24.

Jednak albo opracowanie płaskiego opakowania nie zostało opanowane, albo taki pakiet nie wyciągnął pożądanej częstotliwości (ze względu na indukcyjność wyjść), ale ostatecznie w zakładzie w Donskoj opracowano zupełnie inny pakiet, analog amerykańskiego cerpacka-24, aby rozpocząć produkcję eksperymentalnej partii 1500. pamięci, było możliwe dopiero do 1982 r., A seria - jeszcze później.

Mińsk Integral otrzymał polecenie opracowania TEZ dla tej gospodarki (ROC „Desant-1” i „Desant-2”).

Pierwszy naleśnik wyszedł nierówno, TEZ miały monstrualny gradient temperatury i bezlitośnie zawiodły.

Musiałem opracować drugą wersję płytki i przeprowadzić wstępne sortowanie układu scalonego w niskich temperaturach minus 15-30 stopni, aby można było szybko zidentyfikować uszkodzone egzemplarze. Wymagało to opracowania nowego układu pomiarowego i komór klimatycznych.

W NICEVT w tym samym czasie cierpieli z tymi samymi problemami.

W rezultacie MTBF dla szafy wciąż wynosił około 20 godzin.

Latem 1986 roku nadal wykończono trzy stojaki pamięci, jednak jeden TEZ nie wystarczył w połowie.

Kiedy w ramach projektu „Electronics SS BIS-2” postanowili zwiększyć pamięć RAM o 8 razy, otworzyli nowy dział badawczo-rozwojowy „Desant-3” dla mikroukładów K1500RU470, ale wszystko zakończyło się niczym.

Jak zaprojektować mikrochip?

Przy konstrukcji maszyny sytuacja jest na ogół niezwykle trudna.

Prawdopodobnie ostatnim komputerem Hi-End, który używał metod ręcznych, był Cray-1.

Jak pisaliśmy w poprzednim artykule, Cray był geniuszem minimalizmu, co ułatwiło mu i jego zespołowi pracę.

Całą logikę superkomputera zebrał na jednym elemencie logicznym, dualnym 4OR/5OR-NOT, co pozwoliło wyrazić architekturę w postaci szeregu ogólnie uznanych formuł logicznych (a nie jak własny ezoteryczny język Lebiediewa).

W rezultacie jego pracownicy po prostu ostrożnie przenieśli notatki Cray'a na prawdziwe żetony. Cały ten przepych został zamontowany na pięciowarstwowej płycie, w której tylko 2 górne warstwy były sygnałem, a dolne 5,2 były solidne: -2 V, -XNUMX V i uziemienie. Dwie takie deski zostały złożone jak kanapka na arkuszu miedzi, przez który ciepło było odprowadzane i wysyłane do stojaka.

Pakiet termiczny i pobór mocy obliczono poprzez wyrównanie ilości obudów na płytce, ponieważ wszystkie elementy były takie same. To automatycznie skutkowało równomiernym rozpraszaniem ciepła i zużyciem energii przez szafy.

Warunki wyścigowe były zwalczane skutecznie, po prostu dzięki tej samej długości wszystkich skrętek.

W rzeczywistości Cray-1 był czysto architektonicznie prosty do zhańbienia, a to pozwoliło wykończyć samochód rekordowo małym zespołem i starannie go zmontować bez najmniejszych ościeży, co więcej pod względem osiągów zrobił wszystko, co był na świecie w tym momencie.

Dla porównania: dopiero w 1989 roku ledwo dogonił potwornie nieporęczny i skomplikowany Elbrus-2, którym przez 20 lat transportowano tłum ludzi, mimo że ładowarka Cray-1 była tak prosta, że stary Seymour pamiętał ją przez serce.

Niestety, z wyjątkiem Yuditsky'ego i Kartseva (których maszyny, jak pamiętamy, działały skutecznie nawet na okropnej sowieckiej bazie elementów, nie wymagając wygłupiania się z BMK), radzieccy projektanci kierunku „akademickiego” nie rozumieli idei architektonicznych w ogóle prostota i czystość.

Z punktu widzenia sowieckich instytutów badawczych im trudniej, tym chłodniej, dlatego w końcu ta sama „Elektronika SSBIS” została opisana przez samych jej twórców (już znacznie później, kiedy stało się to możliwe) w następujący sposób:

Według dzisiejszych standardów rozmiar płytki drukowanej jest większy niż rozmiar fajnego laptopa!

Nie pamiętam zasilacza. Zapewne, podobnie jak na Elbrusie, źródła zaplanowano pod podniesioną podłogą.

Moim zdaniem projekt SS LSI był pretensjonalnym g…m nieuzasadnionymi decyzjami. Jeden nonsens chłodzenia freonem był coś wart.

Ale wszystko było bardzo solidne i akademickie i zajmowało połowę stadionu, a nie kilka pokoi, i wydało (teoretycznie) tylko dwa razy więcej Cray-1.

W przypadku samego Cray-1 inżynierowie spokojnie i szybko rozłożyli własnymi rękami 113 rodzajów płytek drukowanych, co umożliwiło ułożenie rozwoju w latach 1972-1976.

Auto zostało zbudowane z oczekiwaniem na kolejne modernizacje, a już w ks. D używał 23 typów układów scalonych i czterokrotnie pojemniejszej pamięci.

W rzeczywistości co sześć miesięcy (do 1985 r.) wypuszczano nową iterację, wykorzystującą tańszą, bardziej zaawansowaną technologicznie i nowoczesną bazę elementów, więc Cray-1 z pierwszych i ostatnich wydań to w rzeczywistości różne maszyny.

W 1972 r. przy superkomputerze pracowało tylko 12 osób - cały personel Cray Research, do 1976 r. było ich 24. Dopiero gdy rozpoczęła się masowa produkcja, musieli zatrudnić około stu instalatorów i inżynierów.

Nawet kiedy wyszedł CDC6600, niezwykle zdenerwowany Thomas Watson Jr., dyrektor IBM, zwołał swoich pracowników i zapytał:

Porównując ten skromny wysiłek z naszą własną rozległą działalnością rozwojową, nie rozumiem, dlaczego straciliśmy pozycję lidera w branży, pozwalając komuś innemu zaoferować najpotężniejszy komputer na świecie. W Jenny Lake uważam, że najwyższy priorytet należy nadać dyskusji na temat tego, co robimy źle i jak powinniśmy natychmiast to zmienić.

Słysząc o tym HistorieCray odpowiedział sarkastycznie:

Niemniej jednak, do 1980 roku stało się jasne, że przy obecnym tempie wzrostu złożoności BMC nie było już możliwości rozłożenia ich własnymi rękami, CAD był potrzebny.

W zasadzie były używane na Zachodzie, choć nie masowo, od 1967-1968. (W szczególności IBM wykorzystał własne środowisko generujące do opracowania projektu S/370 BMK). Fairchild pomyślał o nich w połowie lat 1970. i wypuścił je wraz z F100/F200.

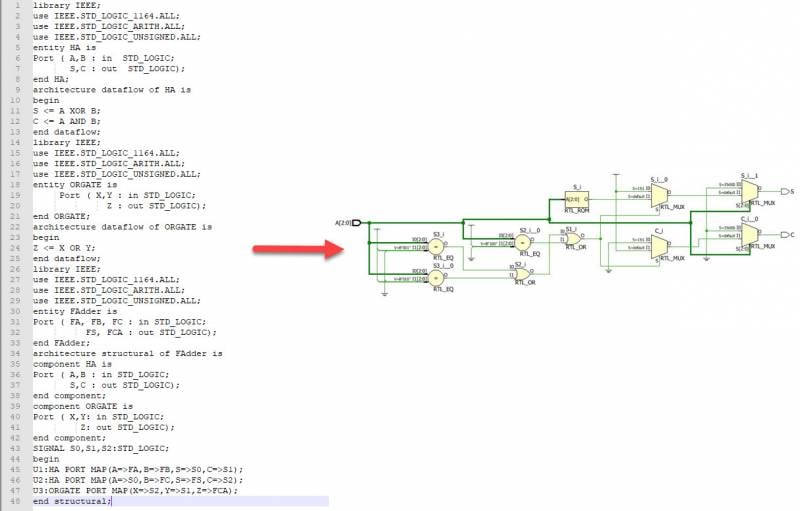

Zaprojektowanie zupełnie nowego komputera (no, albo sklonowanie starego, ale jak w przypadku Elbrusa, z hojną domieszką „ulepszeń”) składa się z następujących kroków.

Najpierw rozwijany jest system dowodzenia (tzw. ISA, jedyne, co mógł zrobić Lebiediew, a nawet wtedy BESM-6 okazał się odrobiną techno-schizofrenii).

Następnie - musimy umieścić system poleceń na prawdziwym krysztale. Pierwszym krokiem jest tłumaczenie ISA na język układów logicznych. Na Zachodzie z reguły używają do tego VHDL, SystemC lub System Verilog, większość tych narzędzi pojawiła się na początku lat 1980. i była nieznana w ZSRR.

Cray, ze względu na prostotę Cray-1, wykonał tłumaczenie ręcznie (Lebiediew w BESM-6 wymyślił również własną nieczytelną notację, w której opisał całą architekturę maszyny), Fairchild opracował własne środowisko projektowe do pracy z F100 / F200 w połowie lat 1970. (zbierał CDC CYBER wszystkich wersji). Wiele firm, takich jak Fujitsu, IBM czy Siemens, oferowało własne autorskie systemy.

To właśnie ten etap odpowiada za zapewnienie, że chip generalnie robi to, czego potrzebuje.

Potem przychodzi etap projektowania obwodu fizycznego.

Na tym etapie realizowana przez nas logika jest testowana dla konkretnego BMC. Oznacza to, że musimy wygenerować fizyczny obwód na podstawie jego opisu, wykonać syntezę zegara, routing itp.

Fizyczny projekt w ogóle nie wpływa na funkcjonalność (jeśli jest wykonany prawidłowo), ale określa, jak szybko działa chip i ile kosztuje.

Na tym etapie można wykorzystać liczne opatentowane algorytmy optymalnego rozmieszczenia elementów logicznych na chipie, często opracowywane przez samych producentów BMC. Uzyskany wynik wymaga oczywiście testów i weryfikacji, co jest często najtrudniejszym procesem.

Pierwszy wydajny algorytm syntezy testów został opracowany przez Johna Paula Rotha z IBM dopiero w 1966 roku. Właściwie wszystkie sowieckie algorytmy testowe były jego kopią lub uogólnieniem.

Gdy zsyntetyzujemy w ten sposób jeden kryształ, procedurę trzeba powtórzyć dla wszystkich podstawowych chipów, z których zmontujemy maszynę – aby zsyntetyzować całą logikę, rejestry, urządzenie sterujące itp. w kryształach.

Gdy tylko to wszystko zostanie umieszczone w BMK (no lub równolegle z tym), zaczynają projektować dla nich płytki drukowane. Konieczne jest określenie ich wielkości, ilości warstw, oddzielenie zasilania i magistral, umieszczenie na nich kryształów. Do trasowania płyt i weryfikacji wyniku wykorzystywane są również własne systemy CAD.

Równolegle z syntezą płyt powstaje konstrukcja do nich oraz układy zasilania i chłodzenia.

W ten sposób powstały wszystkie samochody z lat 1970-1980.

W ZSRR metody projektowania wspomaganego komputerowo zaczęły się rozwijać mniej więcej w tym samym czasie, co w Stanach Zjednoczonych - w połowie lat 1960. XX wieku.

Prawie wszystko, co wiadomo o wczesnych wydarzeniach sowieckich, mieści się w jednym akapicie Małaszewicza:

Nic wiarygodnego nie można znaleźć ani o FOROS, ani o I. Ya.

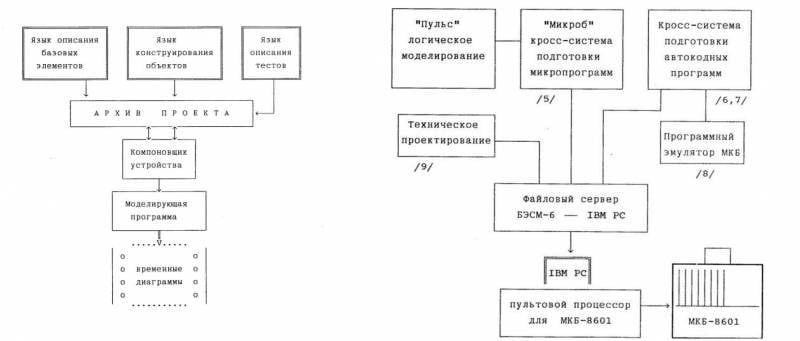

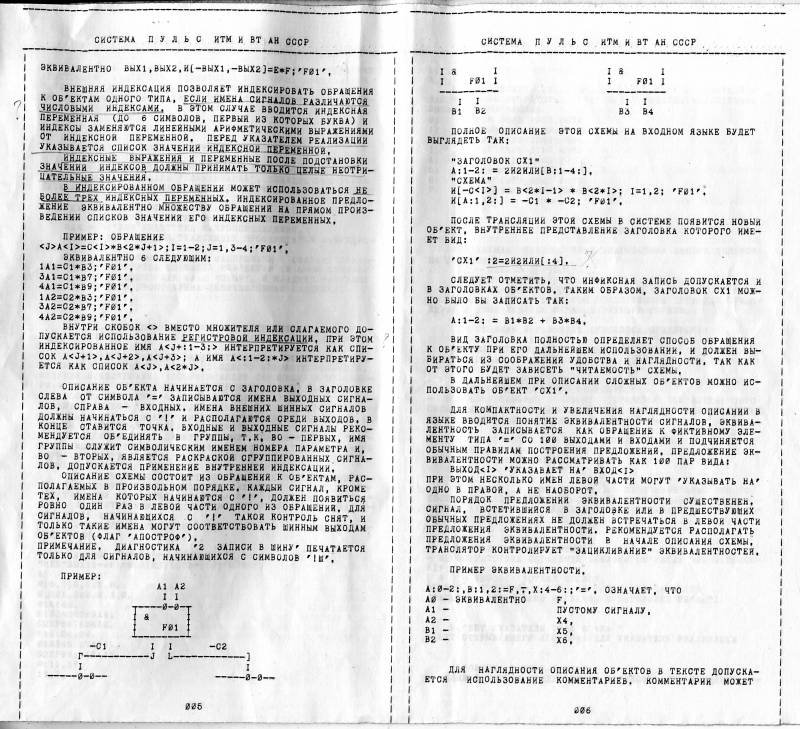

Niemniej jednak niezawodnie wiadomo, że ten PULSE służył do połowy lat 1980-tych, działał wyłącznie na BESM-6 i był niewygodny w użyciu.

D. E. Guryev, który pracował w Delta na 22. piętrze w swoim zoo CAD, wspomina:

Ale rozwojem/utrzymaniem tego produktu zajmował się ktoś inny, nie z naszego działu.

Nasz CAD koncentrował się na inżynierii projektowej. I to nie tylko mikroczipy, ale także płytki, w których powinny być zainstalowane.

Prace naszego systemu rozpoczęły się od tego, że z PULSE zaimportowano schemat logiczny: listę elementów i ich wzajemne połączenia, co, jak rozumiem, w zachodnich systemach CAD nazywa się słowem NETLIST.

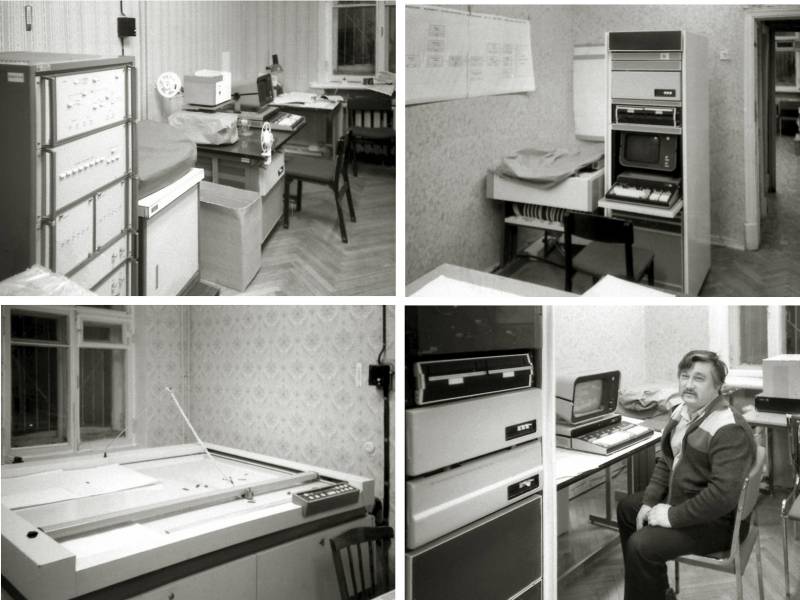

Zarówno PULSE, jak i nasz CAD działały na BESM-6. Miała już wszystkie urządzenia peryferyjne z komputera ES. Maszyna ta była sterowana za pomocą systemu Dispak OS, MS Dubna, zastosowano również system dialogowy JIN.

Nasz CAD posiadał również własne narzędzia do zarządzania procesem obliczeniowym, opracowane w ramach działu, w szczególności specjalistyczny język kontroli zadań oraz system plików (nawet trzy).

Nasz rozwój został przeprowadzony w języku Pascal na kompilatorze A.S. Pirin.

CAD przeprowadził śledzenie obwodów elektrycznych dla bloków i mikroukładów.

Ten zestaw algorytmów został opracowany przez Władimira Susowa i jego mały zespół.

Rozmieszczanie elementów wydawało się być ręczne lub półautomatyczne. W każdym razie nie pamiętam pełnej automatyzacji tego etapu projektowania.

CAD dostarczył dane wyjściowe wyników projektowania na media niezbędne do procesów produkcyjnych. (Nie znam szczegółów wdrożenia, poza tymi, z którymi byłem osobiście zaangażowany, więcej o tym poniżej.)

Osobiście byłem zajęty opracowywaniem podsystemu, który zsyntetyzował testy kontroli wyjścia i wejścia dla I200/I300/I300B. Miałem pre-processing, organizację procesu obliczeniowego, post-processing, analitykę i transformacje optymalizujące.

Krótko mówiąc, wykonałem prawie całą brudną robotę w tym podsystemie.

Oprócz głównego algorytmu, który był bezpośrednio obsługiwany przez A. S. Yaitskova i jego żonę G. A. Yaitskova.

Efektem działania systemu były teksty w języku wejściowym systemu testującego Centry używanego w zakładzie w Zelenogradzie.

Zostały nagrane na taśmę magnetofonową w BESM, a potem, oto i oto, zostały odczytane przez ten burżuazyjny sprzęt i przez niego wykonane.

Aby zapisać na taśmie, musiałem głębiej zagłębić się w polecenia niskiego poziomu do sterowania napędem taśmowym.

Istniał również interfejs, który zawijał zsyntetyzowane testy z powrotem do PULSE i tam zostały użyte jako dodatkowe testy weryfikacyjne projektu, oczywiście modelowane przez PULSE. Podczas tych testów ujawniono kilka błędów projektantów chipów.

Ważną częścią naszego CAD były algorytmy weryfikacji opóźnień, zarówno na poziomie projektów chipów, jak i projektów płytek.

Już przy danej częstotliwości długość przewodników jest czynnikiem wpływającym na prędkość propagacji sygnału, a tym samym na prawidłowe działanie układu cyfrowego jako całości.

Algorytmy oceniały poprawność projektu topologii pod względem propagacji opóźnień i sygnalizowały, gdzie projekt jest zagrożony i co należy naprawić. W te algorytmy zaangażowani byli A. S. Yaitskov i Tatyana Ganzha.

CAD używał dwóch oddzielnych systemów plików: dla tekstów źródłowych CAD oraz dla początkowych, pośrednich i wyjściowych danych projektowych.

Oba systemy zostały opracowane przez Władimira Safonowa.

Alternatywny FS dla danych projektowych został opracowany przez Władimira Susowa.

Tutaj należy wyjaśnić współczesnemu czytelnikowi, że DISPAK OS nie miał ani standardowego systemu plików, ani standardowego edytora tekstu, ani standardowego języka zarządzania zadaniami, a wszystkie te zadania były rozwiązywane na swój sposób w każdym większym zastosowanym projekcie.

SAP nie miał nazwy. W końcu nazwa jest potrzebna dla produktu, który gdzieś zostanie dostarczony. Tutaj nic takiego nie było planowane.

CAD wspierał obecny projekt. Część związana z konstruowaniem testów była w kilku artykułach naukowych określana jako „CAD-Test”, ale była to nazwa tylko w kontekście tych artykułów.

Przyjechałem w 1984 roku.

W tym czasie dział istniał, jak rozumiem, przez około 5 lat i działały już algorytmy śledzenia.

Prace nad testami rozpoczęły się już w mojej pamięci, około 1985 roku, nieco później prace nad weryfikacją opóźnień.

Wyjechałem w 1990 roku.

Wydział kontynuował jeszcze dwa lata.

Następnie jego już niewielkie fragmenty zostały przeniesione do ISP i istniały tam przez kolejne 5 lat.

W rezultacie rozwój dla BMK I200 / I300 został przeprowadzony przez następujące systemy. CAD BASKY (podstawowy zautomatyzowany system sterowania i produkcji) na BESM-6, na I29 opracowano 200 schematów, z których 25 wykonano w krzemie.

BASKY otrzymał dane wejściowe z PULSE i przekazał wynik do TOPTRAN, składający się z 300 tysięcy linijek kodu Pascala. SAPRB (bloki) posłużyły do opracowania TEZ, działały podobnie na BESM-6 i uwzględniono je przy projektowaniu opóźnień sygnału między elementami na płytce PCB i między blokami.

SPIN (interaktywny system projektowania) powstał w celu przekazania dokumentacji opracowanej w Delta Research Institute przedsiębiorstwom przemysłowym, powstał w ramach Electronics 100-25 i 79. Jego główną funkcją było przełożenie projektu oprogramowania z SAPRB na zrozumiały dla NPO Quartz ZAWIESZKA w formacie CAD.

Dla pełni szczęścia – żaden z tych systemów nie był graficzny!

A takich urządzeń nie było.

Wtedy przyjrzałem się zagranicznym systemom CAD – okazuje się, że to przede wszystkim edytor graficzny, a potem algorytmy.

I mieliśmy algorytmy bez krewnych. W sprawie wydania materiałów graficznych niezbędnych do produkcji plansz nawiązano kontakt z zaprzyjaźnioną organizacją (lub firmą aliancką) w mieście Czernogołowka. Mieli odpowiedni sprzęt.

Tak, mieliśmy stacje z wyświetlaczami, ale to były terminale alfanumeryczne.

Praca programistów CAD i inżynierów sprzętu była warunkowo interaktywna. Ale to była praca ze znakami.

Ten sam PULSE służy do pisania formuł określających działanie urządzenia (lub jego modelu), który w nowoczesnych systemach CAD nazywany jest RTL.

Nie było grafiki ze względu na brak odpowiednich urządzeń jako klasy.

Były tylko wyjściowe urządzenia graficzne do przygotowania danych technologicznych do produkcji i już wtedy, pamiętam, były wypożyczane.

Uruchomienie określonego zadania: kompilacja programu, modelowanie obwodu, wykonanie dowolnej operacji projektowej (na przykład śledzenie przewodników), przeszło przez ogólną kolejkę zadań systemu, w której w rzeczywistości znajdowały się elektroniczne obrazy kart perforowanych , a zadania te były wykonywane w trybie wsadowym (tak jakby faktycznie miały formę talii kart).

Western CAD, który pojawił się w naszym kraju pod koniec lat 80. na komputerach osobistych, wyznawał zupełnie inną zasadę: jest przede wszystkim edytorem graficznym, do którego można podłączyć jakąś automatyzację poszczególnych operacji projektowych, a może nie. .

U nas działały automatyczne algorytmy, ale bez grafiki i z ograniczonym udziałem człowieka.

Osoba podała zadanie w formie tekstowej, w niej również oceniał wynik, jeśli mu się nie podobało, zmieniał zadanie i uruchamiał swoją wirtualną talię kart dziurkowanych na nowej.

Wydawało się jednak, że istnieje język kontrolny, podobny do powłoki, ale znacznie prostszy, co pomogło częściowo zautomatyzować ten proces, ale wyniki takich poleceń powłoki lub programów powłoki nadal uruchamiały wirtualne talie kart dziurkowanych.

ITMiVT korzystał z nie mniej mistycznego systemu KOMPAS-82 (i znowu wszyscy nie mają pojęcia, czy ma on coś wspólnego z nowoczesnym Kompasem).

Pracowała nad PULSE i w połączeniu z nim oczywiście nad poprawnym ideologicznie BESM-6, który według standardów lat 1980. był już żywym koszmarem.

Nawiasem mówiąc, PULSE odnotowano również w Dubnej - pod koniec lat 1980. opracowali własną wersję mikro-BESM na mikroukładach (MKB-8601, 4 płytki po około 100 mikroukładów), ale nikt tego nie potrzebował.

Z ciekawych cech architektonicznych PULSE można zauważyć, że został napisany wyłącznie pod DISPACK OS i nic więcej, więc inżynierowie JINR musieli dużo majstrować.

Przenośność była nieobecna jako klasa, ponieważ ponad 300 extrakodów DISPACK ponad 20 typów zostało zakodowanych na sztywno w PULSE, a sam system był dystrybuowany przez jego autorów w postaci biblioteki modułów ładujących, więc samodzielne wprowadzanie zmian wymagało wstępnej detranslacji modułów do autokodu, teraz taka procedura byłaby nazywana disasemblacją .

W rezultacie kule dispakova zostały przepiłowane i zastąpione podprogramami DUBNA OS. Czteromiesięczne zamieszanie nie poszło na marne – system przyspieszył dwukrotnie.

Do 1987 roku ukazała się już 14. wersja PULSE, ale nie wiadomo, czy stała się ostatnią.

W połowie lat 80-tych członek-korespondent W.P. Iwannikow zainteresował się językiem VHDL i podjął szereg kroków w celu wdrożenia go w Delcie. Pod jego kierownictwem była grupa rozwijająca kompilator (i prawdopodobnie system symulacyjny) dla VHDL.

W rezultacie napisaliśmy konwerter z PULSE na VHDL i to było to.

Wybitny, oczywiście, NICEVT. Pracowali tam oczywiście dla UE. Pod nim znajdował się własny natywny CAD - EASP, który był używany w Row-4.

W połowie lat osiemdziesiątych NICEVT okazał się ogólnie najbardziej postępową organizacją.

Po pierwsze, udzielili licencji na klonowanie europejskiego BMK Siemens SH100 (i przekształcili je w 1520XM5, więcej o tym poniżej), a po drugie, wraz z kryształami otrzymali autorski system CAD Siemens AULIS.

Problem polegał na tym, że AULIS został pierwotnie opracowany pod systemem operacyjnym BS2000, który działał na niemieckim analogu S/370 Siemens P1 (i bardziej zaawansowanych). Linia ta nie była rozwinięciem czystego S/360, ale taka sama jak Brytyjczycy, jej klon RCA Spectra 70, zmodyfikowany i niekompatybilny z naszą UE.

Powstaje pytanie - czy NICEVT kupił też niemiecki mainframe?

Lub przepisany CAD dla UE?

Teoretycznie można go również uruchomić na M-4000.

To jedyny klon S/360, z którym NICEVT nie miał nic wspólnego, został nawet oszukany z zupełnie innej maszyny – właśnie tego samego Siemensa 4004, a zrobili to w dawnym Brukovsky INEUM, już przez nas zapomnianym, w latach 1972-1977. Na nim BS2000 teoretycznie mógłby rozpocząć się natywnie lub z minimalnym wykończeniem. Na początku lat 1980. w Moskwie znajdowało się kilkadziesiąt M-4000, mogli używać jednego z nich.

W rezultacie, kiedy NICEVT opanował jednak AULIS w połowie lat 1980., niezawodnie wiadomo, że proces projektowania kryształu skrócił się z 2 tygodni (NII Delta, czysty PULSE) lub 4–5 dni (ITMiVT, KOMPAS-82) do jednego dnia roboczego.

Zagadki radzieckiej serii XM1-XM6

Problem projektowy pogłębił wybór prototypu.

Eurodeputowani niemal jednocześnie skopiowali MCA600ECL dla ITMiVT, gdzie wygenerowali 1521XM1, MCA1200ECL dla NICEVT, gdzie światu zaprezentowano 1521XM2 i 4.101VZh3, oraz F200K Gate Array, z której narodził się KH1520XM1.

Później opracowano tylko BMK kompatybilne z serią 1500.

Oczywiście taka liczba równoległych projektów nie mogła nie wpłynąć na ich jakość i harmonogram.

Obraz dodatkowo pogarszał fakt, że sądząc po arkuszach danych, 1521XM1 był trochę kompilacją Frankensteina podrobów MCA600ECL i urządzeń peryferyjnych firmy Fairchild FGE.

Zabawne, że w 1993 roku Burcew (kiedy stało się to możliwe) osobno przeszedł przez system sowiecki w swoim memorandum o Elbrusie-2 w Rosyjskiej Akademii Nauk:

Znowu jest rok 1993!

A nasze schematy nie są w pełni opanowane.

Jednak, jak już powiedzieliśmy, cały ten bałagan wokół rozwoju doprowadził do tego, że ostatecznie projekt się nie powiódł, wszystkim (oprócz Babajana i Ryabowa) udało się zdobyć kapelusz, a pozostałe lata ich życia, korzystając z wolności przemówienie, wyjaśnił swój stosunek do siebie.

"Elektronika SSBIS" również doświadczyła zmiany w bazie pierwiastków, ogólnie ludzie z "Delty" zaczęli zagłębiać się w temat z BMK w regionie 1979 (co dało początek plotkom, że opus magnum MEP był przykrywką dla kolejny ściśle tajny projekt wojskowy, choć o Elbrusie znamy wystarczająco dużo i wydawałoby się, że jest znacznie bardziej tajny niż machina tarczy antyrakietowej naszej ojczyzny).

W rezultacie strasznie się trudzili ze śladem I200, używając wszelkich możliwych środków, od gołych rąk (na początku) do PULSU.

Po długich i różnorodnych eksperymentach, stosy potłuczonych kryształów i niedziałające prototypowe płytki, według wspomnień weteranów:

Ale coś opartego na I200 jednak zaczęło się pojawiać, chociaż po 1981 roku zdecydowano się na bardziej zaawansowany I300 - klon serii FGE300 Fairchild F2000 (na 2 zaworów).

Tak pojawiły się mikroukłady K1520XM3 (kryształ I300b), już wyłącznie dla europosła.

Druga iteracja poszła fajniej, w 1984 roku nie było nawet dla nich przypadków, ale do 1985 roku prototyp "Electronics SSBIS" został wystawiony do testów.

Właśnie w tym momencie zarówno Przyjalkovsky, jak i Burtsev zostali po raz pierwszy pobici przez eurodeputowanego.

Przyjałkowski wspomina:

Jednocześnie udało się przekonać ministra przemysłu radiowego P. S. Pleszakowa, że budynek Politechniki MCI o powierzchni 21 tys. m, którego budowa została zakończona przez Ministerstwo przy pomocy NICEVT na terenie NICEVT, wskazane jest przeprofilowanie go w celu opracowania i produkcji specjalnych LSI dla MCI, w tym matrycowych.

Po uzyskaniu zgody ministra kierownictwo NICEVT obsadziło nowy kompleksowy wydział i przy pomocy ministerstwa wyposażyło go, opanowując nowe obszary.

Na początku 1985 r., pomimo niewystarczająco rozwiniętej technologii i niskiej jakości podstawowych kryształów dostarczanych od MEP, na NITsEVT zaczęły pojawiać się pierwsze działające matryce LSI z serii I-300.

W 1984 r. wysiłki NITSEVT zakończyły się sukcesem, niezależnie zaprojektowali, spakowali i wyprodukowali pierwszy układ scalony na I300b, zainstalowali go jako eksperyment w EU-1066 i uruchomili!

IS otrzymał tymczasowy indeks 4.101VZh3 i był funkcjonalnym analogiem Melnikovskaya KN1520XM3.

Najprawdopodobniej znowu musieli kupować skrzynie próbne od Japończyków (którzy w tamtych latach próbowali rozszerzyć swój rynek kosztem Unii, zdławieni przez Reagana i zaczęli powoli pluć na KoK, Toshiba potajemnie prowadził ZSRR jego precyzyjne maszyny do obróbki śrub okrętowych).

NICEVT hojnie podzielił się tym, co zostało wykonane z ITMiVT, ponadto ich zespoły programistyczne zasiadły razem na Varshavka w pomieszczeniach trzeciego złożonego działu NICEVT.

Z kryształem bawiono się dość długo, aż do późnych lat 1980. oryginalna wersja była podatna na samowzbudzenie stopni wejściowych na pasożytniczych reaktancjach wyjść. W rzeczywistości wykonano tylko kilka partii testowych, które trafiły do nie mniej próbnych maszyn.

W rezultacie technologia ewidentnie pozostawała w tyle o 8–9 lat, zamieniając już zmontowane prototypy w dynię.

Ciekawostką jest, że ten sam legendarny budynek w tym momencie był w ciągłym ukończeniu (i ostatecznie nigdy nie został ukończony w zamierzonej formie).

Denis Rodomin, specjalista od architektury radzieckiej, mówi:

Dom w formie dużego łuku miał stać się częścią dużego kompleksu instytucji naukowych.

W centrum tego zespołu planowano wybudować wieżę.

Ale w końcu narodził się tylko „leżący wieżowiec” i dwa kolejne łuki architektoniczne bliżej obwodnicy Moskwy.

Projekt kampusu naukowego nie otrzymał odpowiedniego finansowania: nietypowe konstrukcje wymagały szczególnej uwagi i dużych środków.

W rezultacie niektóre elementy budynku musiały powstać przy użyciu iście rzemieślniczych metod, a budowa się opóźniła.

Dom został oddany do użytku dopiero pod koniec lat 80-tych.

Wewnątrz wyraźnie różnił się od pierwotnego projektu.

Jeszcze smutniejszy los spotkał ich konkurentów z eurodeputowanego.

Już nie leżący, ale całkiem tradycyjny wieżowiec - pomnik poczucia wielkości Shokina.

W 1967 roku architekt Novikov zaproponował wybudowanie dla europosła dwóch wież o wysokości 24 i 20 pięter, projekt był wielokrotnie przerabiany, przekładany i zaczął być realizowany w formie okrojonej dopiero w 1985 roku, a do 1991 roku udało się to dopiero wykończenie okładziny.

W rezultacie niedokończony budynek został zakupiony przez Łukoil na swoją siedzibę, zamieniając go w jeden z najbrzydszych budynków w Moskwie.

Zabawne jest również to, że z trzecim konkurentem, Delta Research Institute, zdarzyła się ta sama historia, ale oni byli najszczęśliwsi ze wszystkich, cóż, ich ojciec, Biuro Projektowe Inżynierii Półprzewodników (KBPM), był bardzo gruby i tajny.

Nie ma o nich informacji na Wikipedii i prawie nic nie wiadomo.

Powstała już w 1961 roku i zajmowała się „opracowywaniem i produkcją specjalnego sprzętu do montażu urządzeń półprzewodnikowych” – to wszystko, co o nich wiemy.

Od 1978 roku specjalizuje się w łączności specjalnej, w tym w systemach światłowodowych.

W 1977 roku wyróżniała się wśród nich „Organizacja PO Box 3390”, o której również nie ma zbyt wielu informacji, poza tym, że jest to laboratorium inżynierii półprzewodników przy KBPM, które otrzymało cywilną nazwę Delta Research Institute.

To właśnie w tym tajnym trenczu Elbrusa poszli Melnikov i jego zespół.

Siedziba główna Delta, modernistyczny wieżowiec przy autostradzie Shchelkovskoye, zaczęto budować w 1971 roku według japońskiego projektu, niezwykle niezwykłego we wszystkim, łącznie z układem wewnętrznym.

Niestety, japoński projekt nie chciał stać na rosyjskiej ziemi i zaczął się toczyć, co udało się ukryć, dodając 2 kolejne mniejsze tomy z boku.

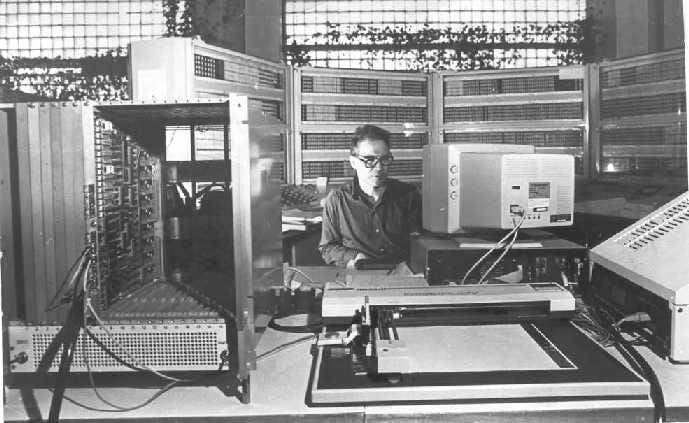

Został wzniesiony epicki, od 1971 do 1983 roku, w wciąż niedokończonym budynku i pracował nad „Elektroniką SSBIS”.

Nawiasem mówiąc, ta sama „Delta” była zaangażowana w mikroukłady, nie tylko wojskowe, piątej akceptacji, ale nawet dziewiątej - produkty specjalnej klasy, używane tylko w satelitach szpiegowskich i specjalnej komunikacji Kremla.

Na dachu (bezprecedensowy dla ZSRR) zainstalowano lądowisko dla helikopterów!

W 1983 roku zakres działalności instytutu badawczego został poszerzony o pion naukowy techniki światłowodowej, który w 1984 roku został przekształcony w samodzielną instytucję.

W 1986 r. utworzono Delta NPO, która oprócz instytutów badawczych obejmowała ich fabrykę w Elling i fabrykę Disk w regionie Oryol.

Projekt SSBIS Electronics był osobiście nadzorowany przez wiceministra Kołesnikowa, a dyrektorem Delta był na ogół syn Shokina.

Mielnikow również nie mógł nie zostać dyrektorem i kierował Instytutem Problemów Cybernetycznych Akademii Nauk ZSRR, utworzonym w 1983 roku, gdzie zaciągnął swojego przyjaciela i kolegę do projektu AS-6 W.P. Iwannikowa, który kiedyś pracował nad pierwszy i gęsty system operacyjny dla BESM -6 - D-68.

Teoretycznie IPK miało skupić się na rozwoju oprogramowania dla „Elektroniki SSBIS”, w praktyce starsi naukowcy robili to, co kochali – intrygi i rozwój funduszy.

Jeden z uczestników tamtych wydarzeń wspomina:

Jak się później okazało, w ciągu roku zespół około sześciu osób wyprodukował więcej oprogramowania niż cały Instytut Programowania Systemowego Iwannikowskiego w okresie pięciu lat.

Zrobiłem kompilator C, asembler, linker. Symulator, biblioteki matematyczne.

W rezultacie Iwannikow zabrał Vitya Janitsky do swojej szkoły podyplomowej, próbował zwabić innych.

Odwiedziłem ich, rozmawiałem z twórcami systemu operacyjnego.

Ale wrażenie było zgniłe i straciłem zainteresowanie projektem.

Nawiasem mówiąc, IPM nie zdołał opanować OS SSBIS, a także napisać przynajmniej czegoś, co dla niego działa.

Ale w 1984 roku Iwannikow został wybrany członkiem korespondentem Akademii Nauk ZSRR, a po śmierci Mielnikowa w 1993 roku kierował Instytutem Programowania Systemowego (ISP) Rosyjskiej Akademii Nauk, utworzonym na podstawie IPC .

„Szczęście” miał też budynek IPK (obecnie zajmowany przez NIISI RAS).

Powstał w legendarnej dzielnicy Novye Cheryomushki, gdzie planowano zbudować cały kampus akademicki, począwszy od budowy największego Domu Książek na świecie, a skończywszy na kilku instytutach badawczych wzdłuż Prospektu Nachimovsky.

Grała jednak ta sama klątwa lat 1980. – prawie nic nie dokończono (Dom Księgi został zbudowany według amerykańskiego projektu na olimpiadę, ale wraz z wybuchem wojny afgańskiej budowa została wstrzymana, a ukończono ją dopiero w pod koniec lat 1990.).

Do 1991 roku budynek IPK został ukończony w połowie (pomimo tego, że zgodnie z dokumentami był to 100% - nie miał dekoracji, windy nie działały itp.), a wszelkie nadmierne wydatki zostały hojnie uwzględnione w budżecie SSBIS Electronics.

Pomimo tego, że NIISI RAS jest teraz ozdobiony dumnym napisem „Tu pracował akademik Mielnikow”, praktycznie nie pojawił się w najbardziej niedokończonym budynku.

Biorąc to wszystko pod uwagę, nie dziwi plotki o ściśle tajnych projektach Delta, dla których Electronics SSBIS służył jako przebranie, a także fakt, że do 1991 roku otrzymywał praktycznie nieograniczone finansowanie, przewyższając nawet Elbrus-2.

Zrozumiałe jest też tajność, przewyższająca nawet systemy obrony przeciwrakietowej (przecież tu dokonano oczywiście pewnych zmian dla samego Biura Politycznego, w tym łączności specjalnej), i dlaczego europosłanka tak uparcie trzymała się Elektroniki do końca.

Ogólnie historia Delty jest niesamowicie mętna.

Oto, co powiedział o tym jeden z tych, którzy próbowali odkryć temat przy tworzeniu „Elektroniki SSBIS”:

Prawdopodobnie nie wyobrażasz sobie nawet reakcji ludzi, gdy zaczynają z nimi rozmawiać na ten temat z dokumentami i artefaktami w rękach.

<…>

Tak, wtedy dość powszechną praktyką było umieszczanie na liście autorów, którzy nie byli zaangażowani i wykluczanie osób odpowiedzialnych za kreację.

Ale trzeba wziąć pod uwagę, że na tych listach są ludzie od prostych inżynierów po akademików, przy tym drażliwych...

Jest bardzo prawdopodobne, że ta historia nie została tylko wyciszona ...

Ciekawa informacja do zastanowienia, przeszukuję strony internetowe z życiorysami i gdy znajdę osobę, która szuka pracy z wierszem o uczestnictwie w projekcie BIS CC, dzwonię na 12 osób, z którymi rozmawiałam jako potencjalny pracodawca, tylko 2,5 ludzie byli rozsądni , a potem z przerażeniem zdajesz sobie sprawę, że Gurkovsky najprawdopodobniej ma rację, a nie z gniewu mówi, że kiedy przybył do Delty w 81 roku, był tłum, który był 20 lat za obecnym poziomem w tym czasie, wyobraź sobie moją szczerą traumę, gdy rozmawiałem z ludźmi, którzy utknęli w latach 60. z BESM-6 i modnymi młodzieżowymi urządzeniami, takimi jak komputery ASP-6 i Bull w głowach, oraz historie, które chcieli opowiedzieć w tajemnicy, jak NITSEVT zniszczył sowiecką VT!

I tak, obraża ich życie, że ich zasługi nie są doceniane, nie mogą znaleźć pracy itp.

<…>

I tak, zupełnie zapomniałem, źródła dzielą się na trzy typy, zdecydowana większość tych, którzy pozycjonują się jako twórcy SS LSI, w ogóle nic nie rozumie, nie jest jasne, jak mogłyby działać, pozostała część mniejsza jest przeze mnie cytowany dosłownie, ale ich stosunek do sprawy widać z cytatów, mniejszość przytłaczająca typ Gurkowskiego dosłownie w kilka minut jest gotowa włamać się do nieprzyzwoitych słów, gdy mówi o tym, co się dzieje...

Jedno z niewielu adekwatnych wspomnień z Delta Research Institute pochodzi od osoby, która po prostu nie pracowała w grupie Mielnikowa:

Był to pierwszy dział (a dział, w którym pracowałem, był zarówno drugim, jak i trzecim).

Pierwsza była najważniejsza (prestiż, pensje pracowników, lokalizacja w naszej wieży przy autostradzie Schelkovskoye, moim zdaniem 2, a także łączna liczba pracowników, ale nie jestem do końca pewien co do drugiego).

Nie wykluczam, że Mielnikowici mieli też inne stanowiska.

W każdym razie wszelkiego rodzaju priorytety były dla nich znacznie wyższe. Ich nadrzędne znaczenie zawsze było deklarowane.

Innymi słowy, uważano, że Mielnikow i Spółka jest państwem w państwie.

Nie było w zwyczaju do nich chodzić.

Coś w tym stylu.

Moi bliscy współpracownicy i ja byliśmy (i nadal jesteśmy) ludźmi analogowymi, podczas gdy wszyscy są cyfrowi…

Nie było dużego zainteresowania.

Pamiętam tylko, że „WSZYSTKO TO” zrobiło się tam bardzo gorąco (podobno były problemy z rozpraszaniem mocy).

Dokonali też obliczeń na BESM-6, z których mieli mnóstwo dobrego, i działali dobrze, nie zawieszali się (w przeciwieństwie do naszego super-buggy ES-1060, który został szybko zastąpiony przez rentowny GDR ES-1055M, na w którym jednak pojawił się na zawsze pamiętny PELICAN, który był adaptowaną wersją SPICE2.G6.

Pamiętam też, że krążyły plotki, że sama nazwa „Delta” oznacza rodzaj triumwiratu, w którym głównym szczytem są Melnikowici i musielibyśmy dla nich zrobić mikroukłady i jeszcze jeden szczyt wzdłuż linii Shokina A. A. (optyczny kanały komunikacji) .

Może tak było zamierzone, przynajmniej biurokratycznie, i brzmi w każdym razie logicznie formalnie.

Mimo to nie zrobiliśmy dla nich żadnych mikroukładów, wyciągnęliśmy naszą starą taśmę.

Teraz jest jasne, dlaczego do 1985 r. Mikron i eurodeputowani w końcu wysłali wszystkich w długą podróż, z wyjątkiem grupy Mielnikowa, w wyniku czego wszystkie inne opracowania MRP zostały przeprowadzone w rzeczywistości niezależnie (i nie było nic za to przez eurodeputowanego - ponownie oceń grubość rażącego uderzenia, jeśli przesłoni on nawet militarny rozwój tarczy nuklearnej ZSRR).

Równocześnie zrozumiała jest rekordowa kwota, jaką europoseł kiedykolwiek zapłacił za zakup produkcji – dla Elektroniki SSBIS za 100 mln dolarów zakupiono całą francuską fabrykę płytek drukowanych (MRP kupiła też fabrykę dla siebie , ale cieńszy - za jedyne 70 milionów).

W efekcie MRP zakończyło się tym, że grupa projektantów z trzeciego oddziału EITCEVT została przeniesiona do odrębnego NPO „Fizyka”.

NICEVT musiało ostro dogonić IBM.

Ich 3081 używało procesora w obudowie MCM, na BMC własnej konstrukcji. Jego odpowiednik, flagowy Ryad-3, ES-1066, został zmontowany tylko na K500 - małym sypkim prochu.

To właśnie zamierzali zrobić w ramach Row-4.

Pierwszym prototypem był EU-1087 - taki sam jak EU-1066, ale TEZ na K500 jest zastąpiony jednym BMK na I300b.

W rzeczywistości był to szkic serii, jak Elbrus-1 dla Elbrus-2.

W latach 1985-1988 zbudowano jeden eksperymentalny komputer. Opóźnienia w produkcji były zrozumiałe - trzeba było przenieść 230 typów TEZ do BMK, co skutkowało około 50 osobolatami pracy (12 osób x 2 miesiące w TEZ w BMK x 4 lata).

Projektowanie śledzenia BMK, podobnie jak w Zelenogradzie, odbywało się głównie ręcznie, weryfikacja była zautomatyzowana. Kryształy na I200 nie nadawały się do takiej pracy - TEZ nie mieścił się w 1 lamp i dlatego musieliśmy sami opracować topologię na I000b.

W sumie na tym krysztale wyprodukowano 3 maszyny - EC-1087, EC-1091 (później przemianowane na 1181, jeszcze później - 1187) i 1195.

EC-1181 miał stać się seryjnym wcieleniem EC-1087, w wyniku czego w 1 roku zmontowano dokładnie 1989 maszynę demonstracyjną, a w rozwój musiała zaangażować się SKB Mińskiej Fabryki, która przekazała kanał procesora do BMK.

EC-1187 miał być pierwszym EC, który został całkowicie przeniesiony do BMK, procesora na jednej TEZ z 4 układów scalonych. W EU-1087 planowali zrobić tylko procesor na BMK, a wszystko inne zabrać z EU-1066.

Z racji tego, że auto było o dwa lata dłuższe niż planowano, do czasu jego ukończenia nikt go nie potrzebował.

Według wspomnień uczestników, NICEVT zainwestował większość swoich wysiłków w całkowicie nowe opracowania trzech maszyn, a mając EU-1087 mieli nadzieję, że jakoś się uda, ale, niestety, okazało się jak zawsze.

W rezultacie EU-1187 została formalnie skompletowana w jednym egzemplarzu, wraz z tym samym jednym „superkomputerem” (bo do tego roku pozostała tylko jedna nazwa) EU-1195 – dopiero do 1995 roku, po prostu kupując BMK od IBM, od 1991 roku nie było z tym żadnych problemów.

Oba samochody nie były nikomu potrzebne z oczywistych powodów.

Planowano również produkcję superkomputera EU-1191, ale prace nad nim przerwano w 1989 roku.

W rezultacie, pomimo heroicznych wysiłków twórców chipów, prace nad Row-4 w Moskwie całkowicie się nie powiodły.

W zasadzie nie była to wina ludzi z NICEVT - po prostu nie mieli wystarczająco dużo czasu, umiejętności i technologii. 20 lat systematycznej pracy we współpracy z IBM - i wynik by się pojawił, ale nie było takiego czasu i takich możliwości.

Dwa kolejne samochody Row-4 zostały wyprodukowane poza Moskwą.

ES-1170 został opracowany w Erewaniu bez powodzenia aż do rozpadu ZSRR.

EC-1130 został opracowany w Mińsku przy udziale specjalistów z Moskwy i Kijowa na podstawie innego klonu - 4-bitowego BSP Motorola. U nas zamienił się w sekcję mikroprocesorową K1800. Sama sekcja została opracowana całkowicie niezależnie od starć stolicy w 1979 roku w Wileńskim Biurze Projektowym i ukończona kilka lat później. Integracja do 1 elementów, częstotliwość taktowania do 000 MHz. Ponieważ twórcy byli jak najdalej od Moskwy, wynik został osiągnięty, samochód trafił do serii, stając się ostatnim radzieckim seryjnym pojazdem UE i jedynym z serii 36, który był faktycznie używany. Łącznie wyprodukowano 4 komputerów.

Stary gawędziarz Babayan, jak zawsze, nie mógł się oprzeć niesamowitym opowieściom:

Projektant tej samej EU-1066 (i kolejnej serii 4), a nie gawędziarz, Jurij Siergiejewicz Łomow, oburza się:

Architektura Elbrus 2 jest superskalarna. Architektura ta była znana znacznie wcześniej niż powstał Elbrus. Był używany przez korporacje CDC i Burroughs. Ta architektura była również używana przez IBM w modelu IBM 360/91 w połowie lat 1960. XX wieku.

Nie oznacza to, że wszystkie problemy tej architektury zostały rozwiązane.

Zastosowanie superskalaru nie tylko zawęża zakres zastosowania komputerów ogólnego przeznaczenia, przenosząc go ze strefy klasy uniwersalnej do specjalistycznej, ale także wymaga znacznego dodatkowego wyposażenia, zwiększa koszty i zużycie energii, a zatem nie było wykorzystywane w projekcie komputerowym ES.

W 1972 roku, po przeprowadzeniu symulacji superskalarnego procesora IBM 360/91, wiedzieliśmy już, że mechanizm umożliwiający permutację operacji jest wciąż bardzo złożony. Z pięcioma lub sześcioma urządzeniami arytmetycznymi nie zwolnił, a kiedy stały się 10-15-20, już się dusił.

Wiedzieliśmy też, że problemem była nie tylko liczba jednostek arytmetycznych, ale ograniczenia architektury SISD. Wraz z rozwojem struktury komputerów o tej architekturze, na czynniki determinujące zakłócenie przepływu poleceń i danych, w tym zakresie wpływ mają takie parametry jak logiczna zależność poleceń, przerwania, rozgałęzienia, konflikty, wzajemne wpływ poziomów obsługi wniosków, strategii dystrybucji, zasobów wykonawczych i strategii zarządzania.

Superskalarny dławi się, gdy logiczna zależność poleceń sięga 5–6. Jeśli w latach 1960. stosowanie tej architektury było uzasadnione wymaganiami takich potworów jak Los Alamos i NASA, które były gotowe ponieść wszelkie koszty, aby rozwiązać swoje problemy, to w latach 1980. architektura SISD wyczerpała się, a inne metody zaczęły osiągnąć wysoką wydajność.

A te stwierdzenia, że architektura superskalarna nie była używana za granicą, bo myśleli o niej dopiero w 1995 roku, są co najmniej sprytne.

Rzeczywiście, w tym czasie Intel zaimplementował superskalar w mikroprocesorze. Tym samym nie wymyślił, lecz uwiecznił końcowy rezultat rozwoju architektury SISD, jednego z największych osiągnięć myśli ludzkiej. Udostępniono ją do domeny publicznej i udostępniono do dalszego szerokiego i rozsądnego wykorzystania.

Wydajność IBM 3083 (wersja jednoprocesorowa), według najbardziej ostrożnych szacunków, jest 1,35 razy wyższa niż Elbrus 2 i 3 razy wyższa niż UE 1066.

Sprawdzone na słynnym problemie z Arzamas.

Czas rozwiązania go dla EU 1066 wynosi 14,5 godziny (akt testów państwowych).

Czas rozwiązania go na Elbrusie 2 to 7,25 godziny, podczas gdy IBM 3083 powinien rozwiązać ten problem w 3,2 godziny, czyli 2,24 razy szybciej.

Dodatkowo IBM 3083 ma jeden stojak, EC 1066 ma 3 stojaki, a Elbrus 2 ma 6 stojaków (dla wszystkich maszyn zabierana jest część środkowa).

Wynik IBM został osiągnięty przede wszystkim dzięki technologiom czwartej generacji. Ale jeszcze większą rolę odegrało twórcze rozsądne podejście do rozwoju.

Twórcy stanęli przed dylematem: albo dwa pełne procesory w dwóch szafach, z których każda była pusta w jednej trzeciej. Umożliwiłoby to uzyskanie maksymalnej możliwej wydajności modelu dwuprocesorowego. Lub wypełnij tę pustą przestrzeń.

Ale co?

Wymyślili procesor bez pamięci - dołączony procesor - i otrzymali w 2 rackach 4 (IBM 3084), a w jednym racku 2 procesorową wersję (IBM 3081), aczkolwiek z nieco obniżoną wydajnością w stosunku do dwóch racków wersja .

Ale umieszczając wariant 2-procesorowy w 4 szafach, zrekompensowali straty wariantu z jednym stojakiem.

Pod jakim mikroskopem Babayan widział dokładną kopię (dokładną zegarową) IBM 1066 w EU 3081?

Wynik był rozczarowujący, Lomov ponownie wspomina:

Matrycowe LSI nie pasowały dobrze do struktur CISC i pozwalały na projektowanie zgodnie z tzw. logiką losową (gdy struktura jest dzielona na puste matryce bez żadnego naukowego uzasadnienia).

Zagraniczne kraje wyszły z tej sytuacji na różne sposoby.

W tym czasie pojawiła się na przykład architektura RISC, która jest mniej krytyczna dla wykorzystania macierzy LSI.

Kilka maszyn czwartej generacji zostało już opracowanych za granicą: seria 470 i 580 firmy Amdahl, komputer M200H firmy Hitachi oraz komputer serii 4300 firmy IBM.

W tych komputerach LSI zastosowano różne typy konstrukcji: kasetowe (komputery serii 4300 i M200H), planarne (komputery serii 470), piętrowe (komputery serii 580).

Do tego czasu nasze technologie umożliwiły realizację tego typu konstrukcji.

Ale obraliśmy ścieżkę minimalizacji licznych problemów podczas projektowania na macierzy LSI i opracowaliśmy technologię linii EC1087-EC1181, modeli czwartej generacji.

IBM w modelach z serii IBM 3080 wręcz przeciwnie, postawił na bezprecedensową komplikację technologiczną, słusznie wierząc, że z powstałych problemów jest tylko jedno właściwe wyjście - stworzenie LSI z sensowną logiką regularną, czyli mikroprocesorami.

Ile lat IBM pracuje nad tą technologią, nie wiadomo, ale gdybyśmy rozpoczęli taki rozwój, teraz wiadomo na pewno, że skończylibyśmy go, gdy nikt go nie potrzebował.

I zrobili krok w tym kierunku, opracowując złożoną strukturę pośrednią - moduł ceramiczny TCM100 (moduł przewodzenia ciepła).

Cała złożoność technologiczna polegała na specjalnej ceramice z 33 warstwami, w której umieszczono 118 gołych chipów (flipchipów), z których każdy zawierał 121 styków.

Moduł został połączony z kolejnym poziomem konstrukcji za pomocą 1 przewodów kulowych. Ten poziom miał 800 36 pinów, które zostały połączone (montaż flipchipów) z modułami TCM000.

Moduły TCM100 były chłodzone wodą.

Nikt na świecie nie był w stanie odtworzyć tej technologii. Dzięki temu IBM wyprzedził nas tak bardzo, że nawet przy najbardziej wyrafinowanej technologii, do której byliśmy wówczas zdolni, nadal nie bylibyśmy w stanie osiągnąć takiej wydajności.

Po tym nastąpiły najbardziej ezoteryczne warianty BMK, o których prawie nic nie wiadomo.

BMK 1520XM5 (seria I-DN, ale nie jest to dokładne) zawiera 8 zintegrowanych elementów (tranzystory i rezystory) lub 900 równoważnych bramek, a także pamięć o dostępie swobodnym (RAM) o pojemności 650 bitów z przestrajalną organizacją i czas dostępu do adresu 512 ns . Wykonane w technologii izoplanarnej.

To w rzeczywistości wszystko, co o niej wiemy, a wiarygodność tych informacji jest nieznana.

Jest tylko jasne, że XM5 po raz kolejny zmienił prototyp - stał się Siemens SH100G Gate Array (podobno europejski klon F100) wraz z czymś o nazwie LSI124. Wraz z kryształem ITMiVT otrzymaliśmy od Siemensa ich system AULIS CAD do okablowania BMK, który umożliwił kilkukrotne zwiększenie wydajności projektowania.

BMK K1520XM6 był już ponownie rozwijany w Delcie dla hipotetycznej Elektroniki SSBIS-2, miał zawierać 10 000 zaworów.

Kryształ nazwano I400 (I400b?).

Sam chip niezawodnie istnieje i kolekcjonerzy go widzieli, ale informacji też jest mało:

Niestety jest niedatowany.

Przed nim natknąłem się tylko na odniesienia do I400.

Kiedy się pojawił, nauka dokładnie nie wie, ale w 1986 roku chłopaki, którzy mieli staż w NICEVT, powiedzieli szeptem, że mamy takie urządzenia, ale o nich Wam nie powiemy i z natchnieniem rozmawiali o romansie pracy ze statecznikami I400, na których topi się cyna.

Statecznik to pusta obudowa mikroukładu, w której znajduje się element grzejny o mocy równej przyszłemu mikroukładowi, są one potrzebne do opracowania projektu płyt i obudów REA, zasilaczy i systemów chłodzenia jeszcze przed ich wydaniem do produkcji .

Ponadto od osób, które latem 86 roku zajmowały się podsystemem masowej pamięci półprzewodnikowej dla już SS LSI 2, udało im się dowiedzieć bardzo interesujących rzeczy.

Rozważane są dwa warianty implementacji równoległego algorytmu dekodowania (80,64, 200) kodu na macierzy LSI I400B i IXNUMX.

Pierwsza wersja urządzenia dekodującego składa się z 32 I200B LSI dwóch typów, podczas gdy urządzenie kodujące jest zaimplementowane na 8 I200B LSI.

Druga wersja urządzenia jest zaimplementowana na dwóch BIS I400.

Czas dekodowania to 10 poziomów logicznych w pierwszym wariancie i 8 logicznych poziomów w drugim wariancie.

Czas kodowania to 6 poziomów dla pierwszej opcji, 4 poziomy dla drugiej.

Urządzenia do kodowania i dekodowania kodu złożonego (80,64) znajdują się w UDVP dla każdej linii dostępowej pamięci RAM.

W monumentalnej 12-tomowej książce Nefiedova można się dowiedzieć, że jej przypadek to już typowa PGA i parametry formalne, to właściwie wszystko…

Jeszcze mniej informacji o mitycznym I500 dla „Electronics SSBIS3”.

Znana jest tylko zawartość pary slajdów o tej maszynie, stworzonej na potrzeby raportu komisji JIHTA RAS z przygotowania propozycji w dziedzinie techniki komputerowej w 1991 r. i opublikowanej po raz pierwszy na konferencji w 2018 r.

Istnieje kilka bardzo, bardzo hipotetycznych bramek I500 30K z opóźnieniem 0,15 ns na suwaku, ale wszyscy bardzo wątpią, czy ich rozwój w ogóle się rozpoczął.

Rok 1991 był generalnie punktem zwrotnym dla Akademii.

Potworne państwowe finansowanie bezużytecznych i szalonych projektów, na które akademicy zbierali pieniądze przez dziesięciolecia, a honory nagle się skończyły i zaczęli rozpaczliwie wychodzić, reklamując nowemu rządowi nie mniej szalone projekty wszelkiego rodzaju „elektroniki SSBIS-2 " i 3, nie uruchamiając prawidłowo nawet pierwszego.

Nowy rząd nie spieszył się z przeznaczeniem pieniędzy na slajdy o „genialnej” architekturze, opisanej w postaci wielokolorowych pudełek ze strzałkami „i tu postawimy super mega-inteligentny procesor”, nowy rząd nie spieszył się , więc bezpiecznik się zmarnował.

Typowa produkcja high-tech w ZSRR, począwszy od dojścia do władzy Breżniewa, wyglądała mniej więcej tak (ze wspomnień Habr jeden z programistówktóry spędził całe lata 1980. w przemyśle kosmicznym):

W Instytucie Badawczym Miar Fizycznych wierzchołek to absurdalny kajdan z powiązaniami z szarą strefą. Aby się chronić, zablokowali awans na szczyt zdolnych ludzi.

I na przykład w latach 80. NIIFI co roku zajmowała się rozwojem swoich mikroukładów CMOS. I za każdym razem kończyło się to niepowodzeniem.

Pamiętam, że ja też podskoczyłem, żeby rozwinąć swój mikrochip, wypełniłem masę biurokratycznej roboty papierkowej i w końcu otrzymałem fundusze… kiedy nagle wszyscy dostali się do tych pieniędzy i podzielili je.

Kierownictwo przekazało sam projekt Michaiłowi Fiodorowiczowi, dokładnie taki strzał, który według CMOS do tej pory się nie powiódł.

I pod koniec tej epopei zostałem zmuszony (jako koń pociągowy) do napisania raportu o osiągniętych pozytywnych wynikach.

Nieco później pracowałem również w Biurze Projektów Specjalnych Turbosprężarek.

Przywództwo tam można scharakteryzować po prostu - złodzieje-maniacy.

A w dziedzinie kompetencji technicznych istniał jakiś rodzaj transcendentnego śmietnika, chociaż Baumanka (wydział E-2, Sins) i TsNIDI (Kotenochkin, Deutsch) w latach 60. wykonali swoje pierwsze projekty, które okazały się lepsze na testach we Francji (początek lat 70.) niż produkty ABB TurboSystems.

Mając to na uwadze, nie dziwi fakt, że tylko Elbrus-1970 i Elektronika SSBIS zdołały zakończyć (z całego niewyobrażalnego zoo projektów sowieckich superkomputerów z lat 1980-1990) do 2 roku i przynajmniej jakoś działały zgodnie z przeznaczeniem. tylko kilka lat " Elbrus.

Nic dziwnego, że szalone projekty Akademii Nauk ZSRR z drugą i trzecią wersją „Elektroniki” i ich rozpaczliwe krzyki o zamkniętych „najbardziej obiecujących” obszarach i zrujnowanych unikalnych rozwiązaniach - jednak zostały oderwane od bajeczny karmnik, do którego dorastali w słodkich sowieckich latach.

Nic dziwnego, że ich wołania i wołania o przytulny ZSRR później, kiedy zostali masowo wyrzuceni z ciepłych instytutów badawczych na uczciwy konkurencyjny rynek i odkryli, że nikt ich nie potrzebuje na tym rynku.

W rezultacie kilku naprawdę utalentowanych ludzi, takich jak Jurij Panczuł czy Pentkowski, bez problemu odjechało do MIPS, Intela itd., podczas gdy los szefów polegał na masowym demontażu potwornych funduszy pozostałych po ZSRR.

Do połowy lat 1990. wszystko, co można było przetopić, zostało przekazane i wydane, 16 000 komputerów UE zamieniło się w 50 ton 24-karatowego złota i setki ton srebra i przepłynęło przez południowe republiki i kraje bałtyckie w nieznanym kierunku na zachód.

Co ciekawe, zwracamy również uwagę na fakt, że przejście na architekturę VLIW w Elbrusie-3 było uzasadnione nie tylko faktem, że w 1985 roku w USA stało się nowym trendem, zamiast maszyn tagujących, ale także faktem, że z monstrualną złożonością superskalar w Elbrus-2" cierpiał piekielnie (i ledwo zdołał przełożyć go na BMK, zabijając około 5 lat).

Ideą VLIW było radykalne uproszczenie architektury procesora, dlatego Babayan pomyślał, że jego grupa ma szansę ukończyć Elbrus-3 za kilka lat.

Niestety, maszyna VLIW nadal okazywała się daleko poza jego kompetencjami, a przed wysłaniem na złom w 1993 roku nigdy nie działała.

To kończy fundamentalną historię sowieckich mikroukładów ECL.

Paradoksalnie im bliżej lat 1990., tym mniej źródeł wiarygodnych informacji.

Ogólnie niewiele wiadomo o serii XM1-XM6 i bardziej godnych technoarcheologów niż autor tej pracy.

Dlatego całkiem możliwe, że w artykule pojawią się błędy lub nieścisłości, prośba tych, którzy mają bardziej istotne informacje na temat tej serii, nie kopią zbytnio autora, ale dodają perełki swojej wiedzy do powyższego.

informacja